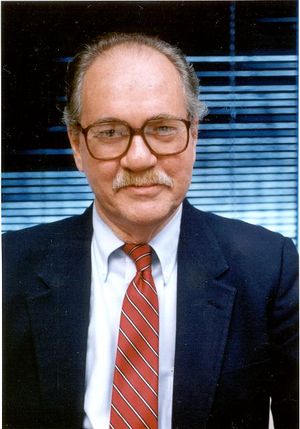

James H. Pomerene

James H. Pomerene

James H. Pomerene was born in Yonkers, New York on 22 June 1920. After receiving the B.S. degree in Electrical Engineering from Northwestern University in June, 1942, he joined the Hazeltine Corporation and was involved with the design of IFF (Identification Friend or Foe) radar working in both the microwave and pulse modulator areas.

In April, 1946, Pomerene accepted an invitation from John von Neumann and Herman Goldstine to join the newly organized Electronic Computer Project at the Institute for Advanced Study in Princeton, New Jersey. This project built a parallel stored program computer that was the prototype for a number of machines such as the Maniac, Oracle, Illiac, etc. Pomerene designed the adder portion of the arithmetic unit and then was entirely responsible for the development and construction of the electrostatic (Williams Tube) memory. In August, 1951, he was appointed Chief Engineer of the project, a position he held until the project was disbanded in 1956.

Pomerene then joined the IBM Corporation in Poughkeepsie, New York where he and several others conducted a study which began the development of the Harvest computer. Harvest consisted of a Stretch computer for standard processing plus a byte vector pipeline unit for processing non-numeric data. Harvest had two levels of program control: one level set up a process, including the pattern for fetching and storing bytes from and to memory, and the second le-.,el operated on that process. It also had a remarkable tape and tape library system, fully automatic and of great capacity.

Following the completion of Harvest, Pomerene studied the use of multiple processors as a way to increase both compute capacity and system availability. In 1965, he headed a team doing the preliminary design of the Parallel Network Digital Computer (PNDC), an early parallel machine. The PNDC was not built, but work on it led Pomerene to the idea of making a highly available memory system out of a number of memory units, each storing one bit position of a word.

Pomerene began a special study of a highly available system based on this memory. As envisioned, the memory would read out a block of words and it was conjectured that this block readout could be useful if each processor in the system were provided with a local memory holding a number of recently used blocks. This arrangement, now known as a cache, was simulated and the results were much better than expected. Subsequently the cache was incorporated in the Model 85 processor. In 1967 Pomerene was promoted to the position of Senior Staff Member at corporate headquarters in Armonk, New York. He was appointed an IBM Fellow in 1976 and soon transferred to the Research Division.

Pomerene was a Life Fellow of the IEEE and a member of the National Academy of Engineering. He authored or co-authored numerous technical papers and one book, and held singly and jointly seventeen patents. Pomerene received the IBM Outstanding Innovation Award in 1968, the IEEE Computer Society's Pioneer Award in 1986, and the IEEE Edison Medal in 1993 "For outstanding contributions to the development of computer architecture, including pipelining, reliable main memory and memory hierarchies". He was married to Edythe R. Pomerene; they had three children, James B., Katherine E., and Andrew T. S. He died 7 December 2008 in Chappaqua, New York.