1st Printing, June 1976 2nd Printing (Rev), October 1977 3rd Printing, August 1979

Copyright <sup>®</sup> 1976, 1977, 1979 by Digital Equipment Corporation

The reproduction of this workbook, in part or whole, is strictly prohibited. For copy information contact the Educational Services Department, Digital Equipment Corporation, Bedford, Massachusetts 01730.

Printed in U.S.A.

# INTRODUCTION TO MINICOMPUTERS

Main Memory

Student Workbook

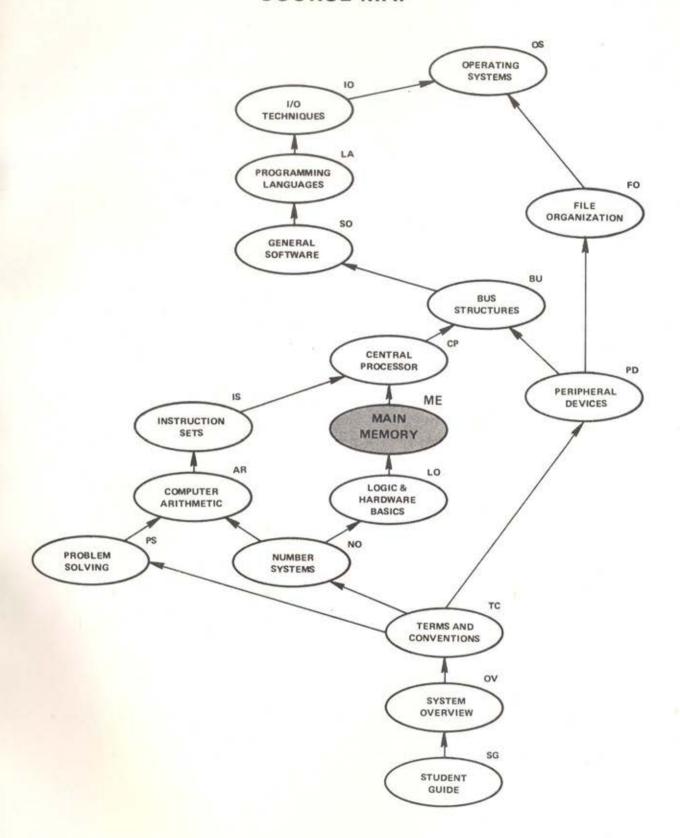

## **COURSE MAP**

# CONTENTS

| Introduction                                    | 1  |

|-------------------------------------------------|----|

| Organization of Main Memory                     | 3  |

| Objectives and Sample Test Items                |    |

| Access Time, Storage Capacity, and Cost per Bit |    |

| Read and Write Operations                       |    |

| Exercises and Solutions                         | 9  |

| Core Memory                                     | 17 |

| Objectives and Sample Test Items                |    |

| Read Memory Cycle                               |    |

| Write Memory Cycle                              | 27 |

| Exercises and Solutions                         | 29 |

| Semiconductor Memory                            | 37 |

| Objectives and Sample Test Items                | 37 |

| Semiconductor Memory Organization               |    |

| Bipolar Memory                                  |    |

| Read Memory Cycle                               | 47 |

| Write Memory Cycle                              |    |

| Metal-Oxide Semiconductor Memory (MOS)          | 49 |

| Comparison of Core, Bipolar, and MOS Memories   |    |

| Exercises and Solutions                         | 53 |

| Improving Main Memory                           | 61 |

| Objective and Sample Test Item                  |    |

| Interleaving                                    | 63 |

| Cache Memory                                    |    |

| Auxiliary Power Supply                          |    |

| Read-Only Memory (ROM)                          |    |

| Exercises and Solutions                         |    |

# Main Memory

#### Introduction

The main memory unit, which holds information used in processing by the central processing unit, is a very important part of the computer. The size and capacity of main memory significantly affect the power and capability of the computer. The larger the memory capacity, the more instructions and information the computer can store internally and, consequently, the faster the computer can perform.

Although various computers employ different types of main memory, the basic functions of memory are all very similar.

The first lesson in this module discusses the general concepts applicable to all types of main memory. The second covers the traditional and most common type of main memory, core memory. The third lesson examines the latest technological advances in main memory, the semiconductor memory, which is rapidly gaining popularity. The fourth and final lesson introduces some of the options currently available to improve the performance of main memory.

# Organization of Main Memory

#### OBJECTIVES -

- Given a table of two types of storage and three storage characteristics and six descriptions, be able to match each storage/characteristic combination with its description

- Given four descriptive statements, be able to label those statements that refer to the read cycle and those that refer to the write cycle.

- Given the four major parts of main memory and four functions, be able to match each part with its function.

#### SAMPLE TEST ITEMS -

The table below presents two types of storage and their characteristics. Complete the table by writing the correct letters in the spaces provided.

### Storage Types

| Characteristic         | Main Memory             | Auxiliary               |

|------------------------|-------------------------|-------------------------|

| Access Time            |                         |                         |

| Storage Capacity       |                         |                         |

| Cost per Bit           | ( <u></u> )             |                         |

| Access Time            | Storage Capacity        | Cost per Bit            |

| a. Slower<br>b. Faster | c. Smaller<br>d. Larger | e. Smaller<br>f. Larger |

|                        |                         |                         |

| -V                           |

|------------------------------|

| read cycle<br>tter in the    |

| /cle                         |

| PRIVICE<br>HTTPZIERE<br>6411 |

| 1000 A                       |

|                              |

|                              |

| tions are                    |

| n                            |

|                              |

|                              |

|                              |

| e <sup>1</sup>               |

|                              |

|                              |

| and the<br>buffer            |

| stores<br>gnals.             |

|                              |

|                              |

Mark your place in the workbook and view Lesson 1 of the A/V program, "Main Memory."

The computer requires vast quantities of information to support its data processing activities. It stores this much needed information in two areas: main memory and auxiliary storage. The data and instructions that are being processed by the central processing unit are held in numbered locations in main memory. Programs and data that are being stored for future use are kept in auxiliary storage. Programs and data can be transferred between main memory and auxiliary storage as often as necessary.

### Access Time, Storage Capacity, and Cost per Bit

The interval of time required to locate and store or retrieve data from a specified memory location is called *access time*. Data and programs stored in main memory can be accessed by the central processor in 1 microsecond or less. Access time for data and programs stored in auxiliary storage is usually measured in tens of milliseconds. This difference is due to the fact that data in main memory can be accessed *directly* by the central processor, while data in auxiliary storage *must be brought into* the computer before it can be used. In addition, data stored in any location in main memory can be accessed in the same amount of time. This is not always true of data stored in auxiliary storage devices.

As the following table illustrates, the differences between main memory and auxiliary storage in terms of access time, storage capacity, and cost per bit are significant.

Table 1 Major Differences Between Main Memory and Auxiliary Storage

|                                | Main Memory      | <b>Auxiliary Storage</b> |

|--------------------------------|------------------|--------------------------|

| Access Time                    | 1 μs or less     | tens of milliseconds     |

| St <mark>orage</mark> Capacity | 4K to 128K words | millions of words        |

| Cost per Bit                   | 0.3 to 3.0 cents | 0.1 to 0.001 cents       |

While main memory can be accessed by the processor faster than any auxiliary storage device, cost factors limit its practical size. Since storage capacities of main memories range from 4K to I28K words, and data processing requirements usually demand millions of words of storage capacity, the large bulk of additional data and programs must be stored in auxiliary storage.

Due to the relatively slow access time from auxiliary storage, programs and data for *current* processing are always placed in main memory where they can be retrieved quickly. By swapping data and programs to and from auxiliary storage, the computer system can function at maximum efficiency, utilizing auxiliary storage for inexpensive bulk storage and main memory for high-speed, internal storage.

#### Read and Write Operations

The process of entering or storing information in main memory is known as writing. Whenever information is written into a memory location, it automatically replaces any information previously stored in that location. Therefore a write operation is always a destructive one. Retrieving information from memory is known as reading. Unlike the write operation, the read operation does not alter the contents of the addressed location. As a result, data can be safely read from memory as often as necessary.

Regardless of whether it specifies a read or a write operation, the central processor always sends the address of the desired location to main memory. *Control lines* direct the main memory to perform a read or write operation and allow memory to communicate its status to the processor. To perform these operations, main memories are usually designed with four fundamental parts:

- Medium

- Location Select Circuit

- Read/Write Circuit

- Control Circuit

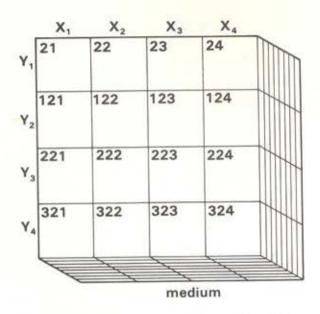

The *medium* physically contains the bits of information during storage. The medium can be considered as a matrix of bits, with each bit indicated by a pair of X and Y coordinates (Figure 1).

The location select circuit identifies the location in the medium required for the next operation and enables it for reading or writing. The location select circuit contains the memory address register, which holds the address of the location being referenced by the processor.

Figure 1 Medium as a Matrix of Bits

Another circuit, the **read/write circuit**, transports the data out of or into the medium. This read/write circuit contains an important register, the memory buffer register, which holds the data on its way to the processor or the data that the processor has sent to be written into the medium.

The final portion of main memory is the control circuit. The control circuit maintains overall internal control of the memory and issues a BUSY signal to the processor during the read/write operation and a DONE signal to the processor when the operation is completed.

The entire read or write operation is known as a *memory cycle*. There are differences in memory cycles among the various types of main memories. These differences result primarily from the medium used to store information. Typical media used in the design of computer storage elements are *magnetic cores*, and *bipolar* and *MOS semiconductors*.

Magnetic core memories have been used extensively since the late 1950s. Semiconductors are a more recent development and are gaining rapidly in popularity. There are other types of main memories, such as thin film and plated wire. However, our discussion of main memories will include magnetic cores, described in Lesson Two of this module, and bipolar and MOS semiconductor memories, which are covered in the third lesson.

1. Fill in the blanks in the table below:

|                  | Main Memory      | Auxiliary Storage |

|------------------|------------------|-------------------|

| Access Time      | 1 μs or less     |                   |

| Storage Capacity |                  | millions of words |

| Cost per Bit     | 0.3 to 3.0 cents |                   |

- 2. What information is stored in main memory?

- 3. Define the following terms as applied to main memory.

- a. Read

- b. Write

- 4. What information does the memory unit require from the CPU in order to perform:

- a. A read operation

- b. A write operation

1. Fill in the blanks in the table below:

|                  | Main Memory      | Auxiliary Storage    |

|------------------|------------------|----------------------|

| Access Time      | 1 μs or less     | tens of milliseconds |

| Storage Capacity | 4K to 128K words | millions of words    |

| Cost per Bit     | 0.3 to 3.0 cents | 0.1 to 0.001 cents   |

2. What information is stored in main memory?

Main memory contains data and instructions used in current processing by the central processing unit.

- 3. Define the following terms as applied to main memory.

- a. Read A read is the process of retrieving information from main memory.

- b. Write A write is the process of entering information into main memory.

- 4. What information does the memory unit require from the CPU in order to perform:

- a. A read operation To perform a read operation, the central processor must send to main memory the numeric address of the desired memory location.

- b. A write operation To perform a write operation, the central processor must send to main memory the numeric address of the desired memory location and the data to be stored therein.

| _     | 3.0  | - | _  | ~     | - |    |

|-------|------|---|----|-------|---|----|

| - 10- | - 10 | - | _  | F - 1 |   |    |

| -     | 1    | _ | п. | v.    | - | ES |

List the four major parts of main memory. Explain the function of each.

- List the four major parts of main memory. Explain the function of each.

- a. Medium The medium contains the memory locations that the processor references with numeric addresses and physically holds the bits of information stored in main memory.

- b. Location Select Circuit The location select circuit decodes the numeric address supplied by the CPU into the X and Y coordinates which indicate the selected word in the medium. It also enables the medium for reading or writing.

- c. Read/Write Circuit During a read operation, the read/write circuit transfers the data out of the medium into the memory buffer register. During a write operation, the read/write circuit transfers the data from the memory buffer register into the medium.

- d. Control Circuit The control circuit receives the read and write commands from the CPU, maintains internal control over the memory unit, and issues a BUSY signal to the CPU when a read/write operation is initiated and a DONE signal when the operation is completed.

|    | - | - | - | -      |

|----|---|---|---|--------|

| EX |   |   |   | Pr 500 |

| -  | - |   |   |        |

| 6. | Specify whether the following statements are to checking the appropriate box.                                                                 | rue or  | false by |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|

|    |                                                                                                                                               | Т       | F        |

|    | The memory address register is located in the location select circuit.                                                                        |         |          |

|    | b. The memory buffer register contains data<br>which is to be written into the medium.                                                        |         |          |

|    | c. Data from any location in main memory can be<br>accessed in the same length of time.                                                       |         |          |

|    | d. Whenever information is read from a memory<br>location, it automatically replaces any informa-<br>tion previously stored in that location. |         |          |

| 7. | List at least two media currently used for main m                                                                                             | nemory  | e.       |

|    |                                                                                                                                               |         |          |

| 8. | The storage capacity of main memory ranges from                                                                                               | m (Circ | le one.) |

|    | a. 1K to 4K words.                                                                                                                            |         |          |

|    | b. 4K to 128K words.                                                                                                                          |         |          |

|    | c. 4K to 512K words.                                                                                                                          |         |          |

|    | d. 4K to 1 million K words.                                                                                                                   |         |          |

| _  | SOLUTIONS                                                                                                                                     |         |       | _  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|----|

| 6. | Specify whether the following statements are checking the appropriate box.                                                                    | true or | false | b  |

|    |                                                                                                                                               | Т       | F     |    |

|    | The memory address register is located in the location select circuit.                                                                        | Ø       |       |    |

|    | b. The memory buffer register contains data<br>which is to be written into the medium.                                                        | Ø       |       |    |

|    | <ul> <li>Data from any location in main memory can be<br/>accessed in the same length of time.</li> </ul>                                     | ¥       |       |    |

|    | d. Whenever information is read from a memory<br>location, it automatically replaces any informa-<br>tion previously stored in that location. |         | Ø     | 85 |

| 7. | List at least two media currently used for main n                                                                                             | nemory. |       |    |

|    | Magnetic cores, bipolar, MOS.                                                                                                                 |         |       |    |

| В. | The storage capacity of main memory ranges from                                                                                               | n:      |       |    |

|    | a. 1K to 4K words.                                                                                                                            |         |       |    |

|    | b 4K to 128K words.                                                                                                                           |         |       |    |

|    |                                                                                                                                               |         |       |    |

c. 4K to 512K words.

d. 4K to 1 million K words.

- What signals does the control unit issue to the processor during read/write operations? (Circle one.)

- a. ON, OFF

- b. BUSY, DONE

- c. START, STOP

- d. PUT, GET

- 10. An entire read/write operation is known as a (circle one):

- a. Control cycle

- b. Memory cycle

- c. Memory module

- d. Read/write circuit

| SO | 11 | IT  | 10 | R.I | C |

|----|----|-----|----|-----|---|

| 30 | _  | , , | ıv | IV  | o |

- 9. What signals does the control unit issue to the processor during read/write operations?

- a. ON, OFF

- **b.** BUSY, DONE

- c. START, STOP

- d. PUT, GET

- 10. An entire read/write operation is known as a:

- a. Control cycle

- (b) Memory cycle

- c. Memory module

- d. Read/write circuit

# **Core Memory**

#### - OBJECTIVES -

- Given six descriptive statements, be able to label those statements that describe major characteristics of core memory.

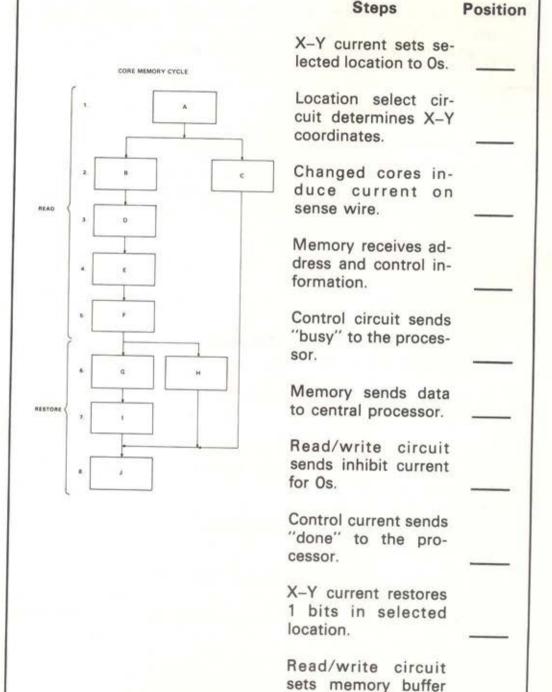

- Given a blank flowchart and a list of the steps in a core memory cycle, be able to match each step with its corresponding position in the flowchart, and write the effect of each step on the contents of the memory location.

#### SAMPLE TEST ITEMS

For each statement below, write a T if the statement describes a major characteristic of core memory. Write an F if the statement does not describe a major characteristic of core memory.

| Statement                                                                                          | T or F |

|----------------------------------------------------------------------------------------------------|--------|

| It is non-volatile.                                                                                |        |

| Each of its core planes includes several sense wires and inhibit wires.                            |        |

| It is composed of iron ferrite cores threaded with wire.                                           |        |

| Any current flowing through an individ-<br>ual core will affect the magnetic field of<br>the core. |        |

| Can perform a read or a write cycle in just one operation.                                         |        |

| Its memory cycle requires both a read and a write operation.                                       |        |

#### 2. Part A

Match each core memory read cycle step with the corresponding position in the flowchart by writing the correct letter in the space provided.

using sense wire.

| C | AB  | ADI  | E - | TEST | ITE | RAC  |

|---|-----|------|-----|------|-----|------|

| 3 | AIN | /1 [ |     | LEGI | 116 | IVIO |

## Part B

Indicate the effect of the above steps on the contents of the memory location by writing N (for nothing), S (for set to 0s), or R (for previous contents restored) in the space provided.

| Steps* | Effect on<br>Memory Location |  |  |

|--------|------------------------------|--|--|

| 1      |                              |  |  |

| 2      |                              |  |  |

| 3      | <u> </u>                     |  |  |

| 4      | 8 <u></u>                    |  |  |

| 5      | : <del></del>                |  |  |

| 6      |                              |  |  |

| 7      | -                            |  |  |

| 8      |                              |  |  |

|        |                              |  |  |

<sup>\*</sup>Steps 2 and 6 are double steps.

Mark your place in this workbook and view Lesson 2 of the A/V program, "Main Memory."

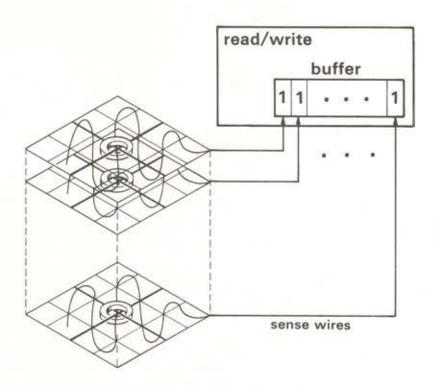

The characteristic that distinguishes core from other types of memory is its medium. Cores are small rings constructed of *ferrite*, a material which can be magnetized. Each core is smaller than the head of a pin, about 1/20th of an inch in diameter, and can contain one bit of information. Over 100,000 cores can be wired together and mounted on a single array or *plane*. These core planes are stacked, one above the other, to form a memory module (Figure 2).

Figure 2 Core and Core Plane

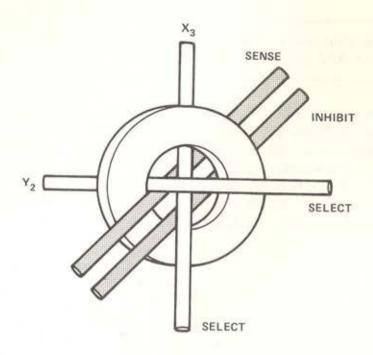

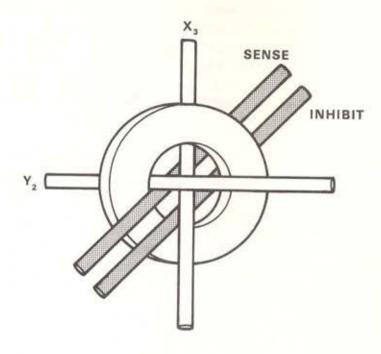

A memory location is a vertical column of cores, one core in each plane, and corresponds to a memory address. The location select circuits decode the addresss held in the memory address register and convert them into X and Y coordinates. These coordinates are represented by individual *select* wires threaded through the appropriate cores (Figure 3).

Figure 3 Four Wires Through a Core

Each core plane also has its own sense wire, which is used for reading, and inhibit wire, which is used for writing. Only one sense wire and one inhibit wire are used for each core plane.

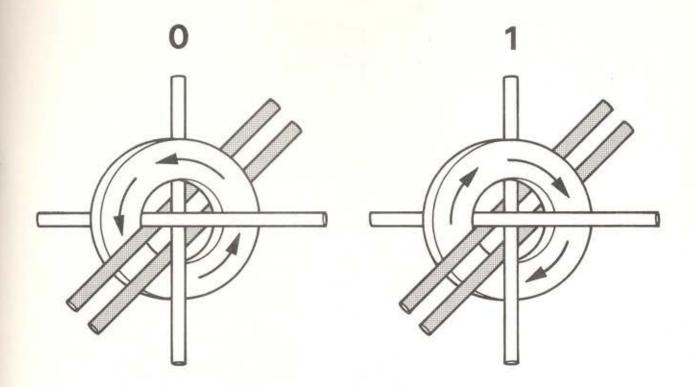

Ferrite cores can be magnetized in either of two directions (Figure 4). The direction of their magnetic field indicates the value of their bit. A counterclockwise field may indicate a zero and a clockwise field may indicate a one, or vice versa. If the total current flowing through a core exceeds a specific threshold, the core is magnetized in that direction. For example, if sufficient current flows up through the core, the core will be magnetized in a counterclockwise direction, representing a zero bit. This zero bit remains in the core until a strong current in the opposite direction changes the core's magnetic field. Any current flowing through a core that does not exceed the threshold value has no effect on the magnetic field of the core.

Figure 4 Magnetized Cores

Reading the bit value of the individual cores is complex because the computer operates on electric current and the information in the core is stored as a magnetic field. However, *changes* in magnetic fields generate electric currents which the read/write circuit can detect. Consequently, reading requires changing the magnetic fields and sensing the change from the electric current it generates.

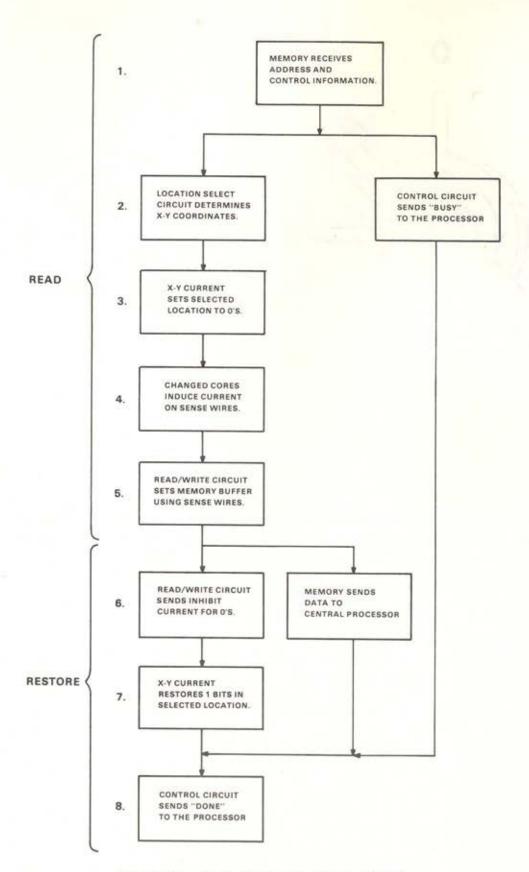

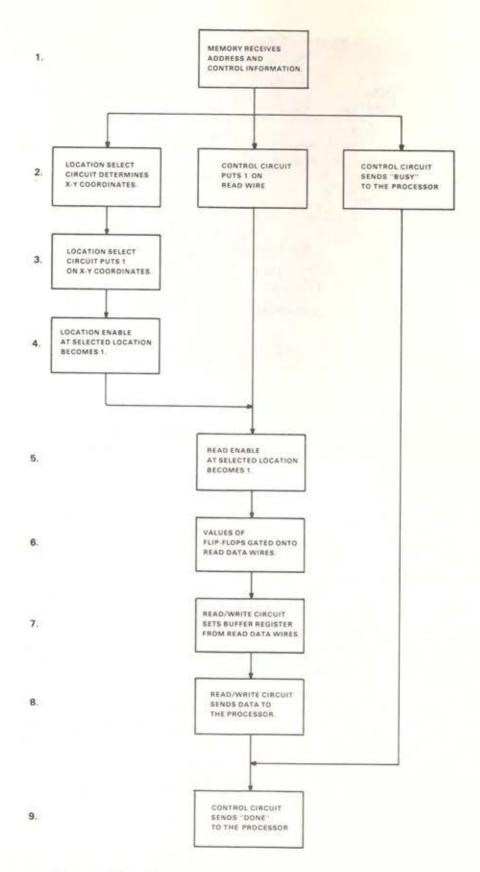

Figure 5 Read Memory Cycle (Core)

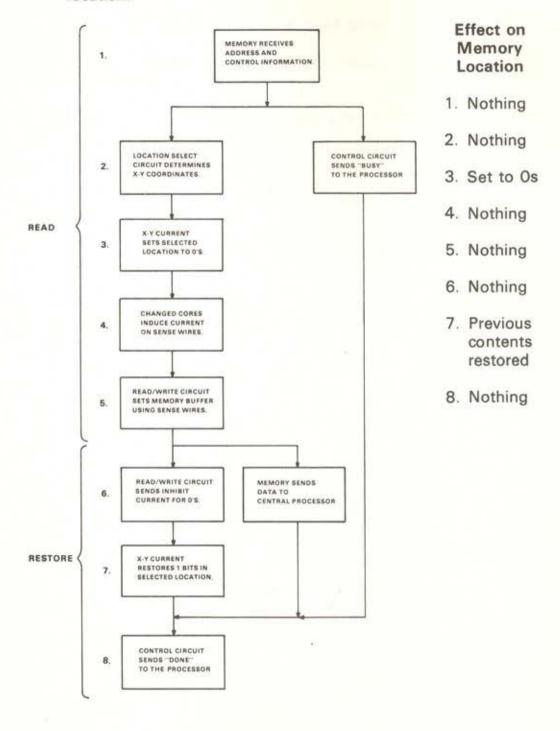

### Read Memory Cycle

A read memory cycle begins when the processor requests information from core memory. The read memory cycle is performed in eight steps as shown in Figure 5.

- A read memory cycle begins when core memory receives from the processor the address of the location to be read and a control signal requesting a read. The address is placed in the memory address register.

- Then, as the location select circuit decodes the contents of the memory address register to determine the X and Y coordinates of the referenced location, the control circuit sends a BUSY signal to the processor. The control circuit will maintain the BUSY status until the memory cycle is complete.

- After the X and Y coordinates of the selected location have been determined, the appropriate wires receive 1/2 the current needed to magnetize a core to ZERO. The cores in the selected location are all set to 0.

- The cores that change to ZERO induce current on the sense wires. These currents are carried on the sense wires to the read/write circuit.

- The read/write circuit sets the memory buffer register to the value of the referenced location using the sense wires. Each wire with an induced current results in a 1 in the buffer register. Wires without induced currents result in 0s.

- As the information is sent to the processor from the buffer register, the read/write circuit also sends inhibit current down the inhibit wires that correspond to 0 bits in the buffer register.

- The X and Y currents are reversed, and the selected bits that have not been inhibited are restored to 1s.

- Finally, the control circuit sends a DONE signal to the processor thus indicating completion of the memory cycle.

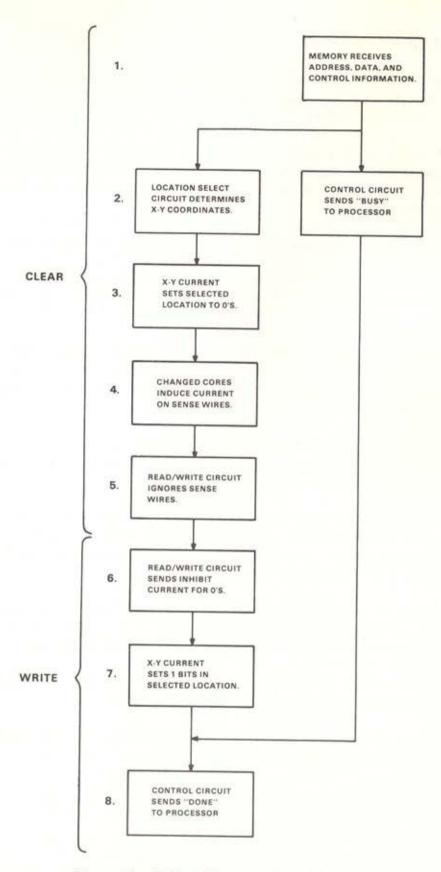

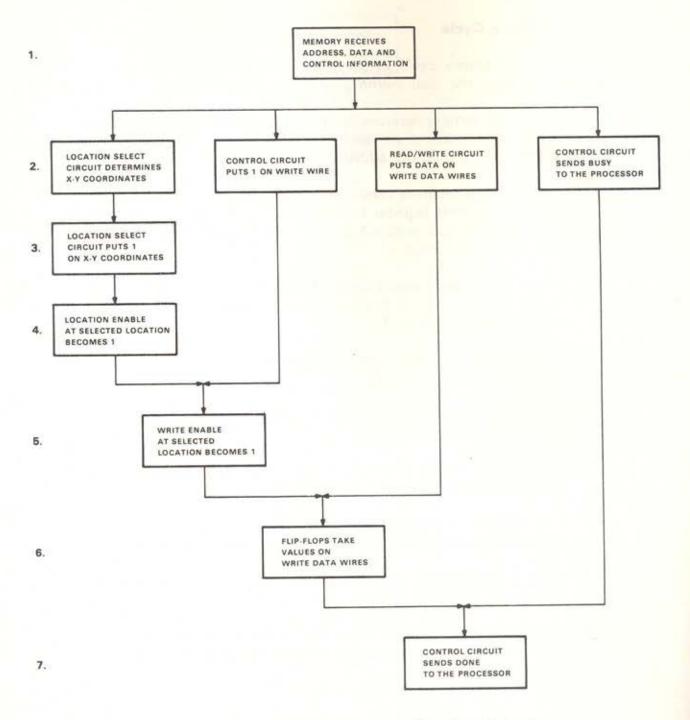

Figure 6 Write Memory Cycle (Core)

#### Write Memory Cycle

The write memory cycle begins when the processor sends information to core memory to be stored. The write memory cycle is also performed in eight steps as shown in Figure 6.

Note that these steps are similar to the steps for a read memory cycle and differ in only a few crucial places. This design allows use of many of the same circuits for both read and write memory cycles.

- A write memory cycle for core memory begins when the address of the location to be written, the data to be written, and the control signal requesting a write are received from the processor. The address is placed in the memory address register, and the data to be written is placed in the memory buffer register.

- Then, as the location select circuit decodes the contents of the memory address register to determine the X and Y coordinates of the referenced location, the control circuit sends a BUSY signal to the processor. The control circuit will maintain its BUSY status until the memory cycle is complete.

- After the X and Y coordinates of the selected location have been determined, the appropriate wires each receive 1/2 the current needed to magnetize a core to ZERO. The cores in the selected location are all set to 0.

- The cores that change to ZERO induce current on the sense wires. These currents are carried on the sense wires to the read/write circuit.

- But during a write cycle, the data to be written is already in the memory buffer register, so the read/write circuit ignores the information in the sense wires.

- After the memory location has been set to ZERO, the read/write circuit sends inhibit current down the inhibit wires that correspond to ZEROs in the memory buffer register.

- 7. The X and Y currents are reversed and the selected bits that have not been inhibited are set to 1, thus writing data into memory.

- Finally, the control circuit sends a DONE signal to the processor, thus indicating completion of the memory cycle.

Obviously, setting the cores to ZERO prior to a write operation and restoring cores to their original state following a read operation are both time-consuming tasks that can slow down the operation of the central processing unit. A typical core memory device can execute a complete cycle in approximately 1 millionth of a second or 1 microsecond, which is slow compared to other types of main memory. In order to use the processor more efficiently, memory cycles can be overlapped with the use of two or more independent core memory units. This process increases the speed of the computer considerably since the CPU can initiate another memory cycle while a restore operation is performed. This procedure, called interleaving, is discussed in Lesson Four of this study unit.

Another feature of core memory is its *non-volatility*. That is, any information stored in core memory remains unchanged when the power is off. In fact, it can only be changed by passing a suitable current through the select wires. This feature is quite an advantage over the other types of memory media which are *volatile* and, consequently, lose their contents when power is lost. Also, core memory consumes very little power. The only time power is necessary is during the actual readand write operations.

Label the following diagram of a core with the X and Y select line, the inhibit wire, and the sense wire.

- 2. What is the purpose of the restore operation in the read cycle?

- 3. Each core plane has its own sense wire which is used for \_\_\_\_\_ and inhibit wire which is used for \_\_\_\_\_.

Label the following diagram of a core with the X and Y select line, the inhibit wire, and the sense wire.

2. What is the purpose of the restore operation in the read cycle?

The restore operation returns the contents of the core to its original value after a destructive read.

3. Each core plane has its own sense wire which is used for reading and inhibit wire which is used for writing.

| -  | -  | EXERCISES                                                                                                                              |         |           |

|----|----|----------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|

| 4. |    | ecify whether the following statements are true or the appropriate box.                                                                | false b | y check-  |

|    |    | 16                                                                                                                                     | Т       | F         |

|    | a. | Reading information stored in core requires changing the magnetic fields and sensing changes from the electric currents they generate. |         |           |

|    | b. | During the restore operation, magnetizing currents are reapplied to the X and Y select lines in the reverse direction.                 |         |           |

|    | C. | An inhibit wire sets the memory location to its original state.                                                                        |         |           |

| 5. | W  | hen the power supply to core is turned off (circle                                                                                     | one):   |           |

|    | a. | The core loses all data.                                                                                                               |         |           |

|    | b. | The 1s are changed to 0s and the 0s are changed                                                                                        | ged to  | 1s.       |

|    | c. | The data remains unchanged.                                                                                                            |         |           |

|    | d. | The sense wire is activated and a BUSY signal CPU.                                                                                     | is issu | ed to the |

| 6. | Fe | rrite cores can store information because (circle                                                                                      | one):   |           |

|    | a. | They can be magnetized in either direction.                                                                                            |         |           |

c. They are insulators and do not conduct electric current.

b. They can conduct electric current in either of two directions.

| 4. | Specify whether the following statements are true or false by checking the appropriate box. |                                                                                                                                        |          |        |  |  |  |  |  |

|----|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------|--------|--|--|--|--|--|

|    |                                                                                             | 54                                                                                                                                     | Т        | F      |  |  |  |  |  |

|    | а.                                                                                          | Reading information stored in core requires changing the magnetic fields and sensing changes from the electric currents they generate. | Ø        |        |  |  |  |  |  |

|    | b.                                                                                          | During the restore operation, magnetizing currents are reapplied to the X and Y select lines in the reverse direction.                 | 4        |        |  |  |  |  |  |

|    | C.                                                                                          | An inhibit wire sets the memory location to its original state.                                                                        |          | Ø      |  |  |  |  |  |

| 5. | W                                                                                           | hen the power supply to core memory is turned                                                                                          | off:     |        |  |  |  |  |  |

|    | a.                                                                                          | The core loses all data.                                                                                                               |          |        |  |  |  |  |  |

|    | b.                                                                                          | The 1s are changed to 0s and the 0s are changed                                                                                        | ged to 1 | S.     |  |  |  |  |  |

|    | ©.)                                                                                         | C.) The data remains unchanged.                                                                                                        |          |        |  |  |  |  |  |

|    | d.                                                                                          | The sense wire is activated and a BUSY signal is issued to the CPU.                                                                    |          |        |  |  |  |  |  |

| 6. | Fe                                                                                          | rrite cores can store information because:                                                                                             |          |        |  |  |  |  |  |

|    | (a.)                                                                                        | They can be magnetized in either direction.                                                                                            |          |        |  |  |  |  |  |

|    | b.                                                                                          | They can conduct electric current in either of tw                                                                                      | vo direc | tions. |  |  |  |  |  |

|    | C.                                                                                          | They are insulators and do not conduct electric                                                                                        | current. |        |  |  |  |  |  |

|        | EXERCISES                                                |          |    |

|--------|----------------------------------------------------------|----------|----|

| 7. Inc | licate whether the following statements are true         | or false | э. |

|        |                                                          | т        | F  |

| a.     | Core memory requires power at all times.                 |          |    |

| b.     | Access time for core memory is measured in milliseconds. |          |    |

| C.     | Each core in core memory stores a single bit of data.    |          |    |

| 7. | Indicate | whether | the | following | statements | are | true or | false. |

|----|----------|---------|-----|-----------|------------|-----|---------|--------|

|----|----------|---------|-----|-----------|------------|-----|---------|--------|

T I

a. Core memory requires power at all times.

b. Access time for core memory is measured in milliseconds.

c. Each core in core memory stores a single bit of data.

## EXERCISES -

8. Draw a flowchart showing the steps for a read cycle. Explain each step in terms of what happens to the contents of the memory location.

8. Draw a flowchart showing the steps for a read cycle. Explain each step in terms of what happens to the contents of the memory location.

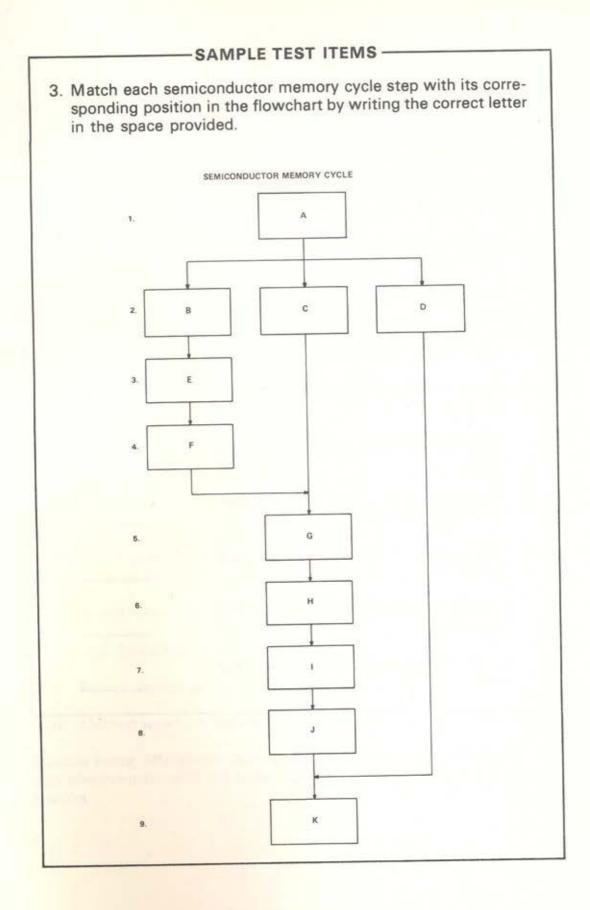

# Semiconductor Memory

## - OBJECTIVES -

- Given six descriptive statements, be able to label those statements that describe major characteristics of semiconductor memory.

- Given a blank flowchart and a list of the steps in a semiconductor memory cycle, be able to match each step with its corresponding position in the flowchart.

- Given a table of 3 memory types, 5 memory characteristics, and 15 descriptions, be able to match each type/characteristic combination with its description.

## SAMPLE TEST ITEMS -

For each statement below, write a T if the statement describes a major characteristic of semiconductor memory. Write an F if it does not describe a major characteristic of semiconductor memory.

| Statement                        | T or F |

|----------------------------------|--------|

| Uses circuit boards.             |        |

| Mass produced on a circuit chip. |        |

|                                  |        |

|                                  |        |

| •                                |        |

|                                  |        |

## SAMPLE TEST ITEMS -

The table below presents types of memory and their characteristics. Complete the table by writing the correct letters in the spaces provided.

|                      | Memory Types |            |      |  |

|----------------------|--------------|------------|------|--|

|                      | Semio        | conductor  |      |  |

| Characteristic       | MOS          | Bipolar    | Core |  |

| Storage Element      |              | r Lastenia | 1111 |  |

| Memory Cycle<br>Time |              |            |      |  |

| Cost per Bit         |              |            |      |  |

| Power<br>Consumption |              |            |      |  |

| Volatility           |              |            |      |  |

| Storage<br>Element | Memory Cycle<br>Time | Cost per Bit |

|--------------------|----------------------|--------------|

| a. Cell            | d. 900 ns            | g. 1-2¢      |

| b. Ferrite         | e. <300 ns           | h. 0.3-0.8¢  |

| c. Flip-flop       | f. 300-800 ns        | i. 0.3-0.5¢  |

# j. High m. Yes k. Low n. No

# SAMPLE TEST ITEMS -

| Step                                                          | Position       |

|---------------------------------------------------------------|----------------|

| Location select circuit determines X-Y coordinates.           | ato ellere les |

| Location select circuit puts 1 on X-Y coordinates.            |                |

| Memory receives address and control information.              |                |

| Control circuit sends "busy" to the processor.                | -              |

| Control circuit puts 1 on read wire.                          |                |

| Location enable at selected location becomes 1.               |                |

| Control circuit ends "done" to the processor.                 |                |

| Read/write circuit sets buffer register from read data wires. |                |

| Read enable at selected location becomes 1.                   |                |

| Read/write circuit sends data to the processor.               |                |

| /alues of flip-flops gated onto read data                     |                |

Semiconductor memory is rapidly becoming the most popular type of medium for the construction of main memory. This is due to a number of important factors, two of which are lower costs and higher speed.

- Lower Costs. Semiconductors store information electronically.

This results in simplified circuitry that can be mass produced.

Semiconductors come in simple, inexpensive, easy-to-assemble units that fit almost any new computer design.

- Higher Speed. Semiconductors perform a read or a write cycle in just one operation.

There is, however, one major disadvantage inherent in semiconductors: *volatility*. Since they store information electronically, when there is a loss of power, information stored in semiconductor memories is completely lost.

Mark your place in the workbook and view Lesson 3 of the A/V program, "Main Memory."

There are two types of semiconductor memories in current use, bipolar and metal-oxide semiconductors (MOS). The major differences between these two types of semiconductor memories are:

- a. Speed (Memory cycle time)

- b. Cost (price per bit)

- c. Power consumption

- d. Method in which they hold information.

Despite these differences, both types of semiconductors store information electronically and are organized as a memory media in a similar fashion.

## Semiconductor Memory Organization

Like the other logic components in the computer, the semiconductor memory unit is composed of a number of integrated circuit (IC) chips mounted on a printed circuit board. A typical semiconductor memory unit consists of semiconductor memory integrated circuit chips, location select logic, and read/write and control logic, all of which may be mounted on one or more printed circuit boards.

The location select circuit selects the memory chips which contain the bits of the referenced location; the read/write circuit performs a read or write operation; and the control logic controls the entire sequence.

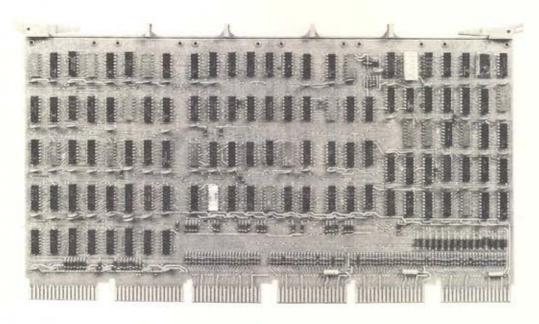

Figure 7 illustrates a typical printed circuit board used in semiconductor memories.

Figure 7 Printed Circuit Board

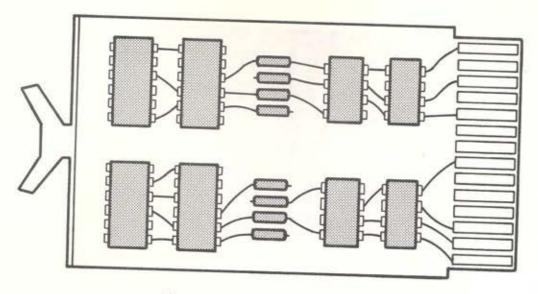

As can be seen, this board is extremely complex. Consequently, a simplified drawing of a 4K 8-bit memory board (Figure 8) will be used to study the structure and organization of a typical semiconductor memory board.

Figure 8 Simplified Board

The board is laid out in rows and columns of semiconductor memory chips that store the information, a group of integrated circuits that handle the read/write functions, another group of chips that handle location select logic, and finally, a group of chips that perform the control operations.

In semiconductor memories, the read/write circuitry and the control unit operate in much the same manner as in core memory. However, the location select circuit on the semiconductor board is not as extensive because the semiconductor memory chips are capable of performing a number of logic functions themselves, whereas core memory does not have that capability.

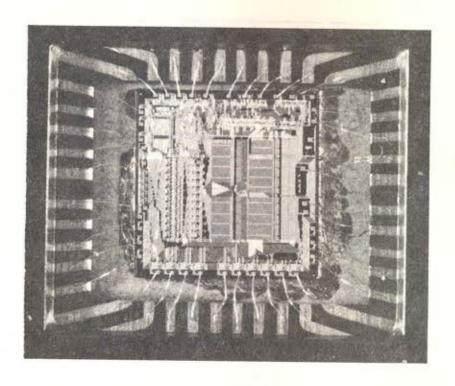

The chips on a semiconductor board range in bit capacity from 1K to 4K. As 1K is a common size, a photograph of one of these chips is given in Figure 9 so that you can examine it in detail.

Each storage element on a semiconductor memory chip is analogous to a core on a core plane. These storage elements are combined to form memory locations that are selected by the X and Y coordinates. Unlike the X and Y coordinates used in core, which must receive half current, the X and Y wires in semiconductor memories carry a binary 1 or 0 as do the standard logic circuits. Now let's examine the specific attributes of each type of semiconductor memory.

Figure 9 1K Semiconductor Memory Chip

## Bipolar Memory

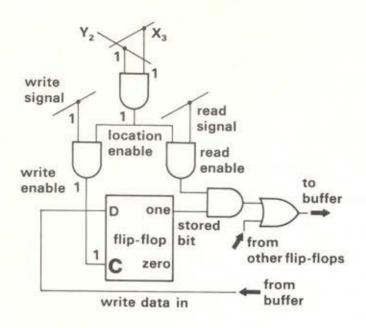

The basic storage element in bipolar memory is a flip-flop. The flip-flop is the same storage element found throughout the computer in registers, counters, and the like. Each flip-flop can store one bit of information just as a core can. It stores information electronically as opposed to a core which uses magnetization.

Figure 10 contains a diagram of a common flip-flop used in semiconductor memory to store a bit of information. Also shown is the logic to read information from and write information into the flip-flop.

Figure 10 One Bit of Bipolar Memory

Now, let's step through the read and write cycles to see how the circuit works. Note that each cycle contains only a read or a write operation.

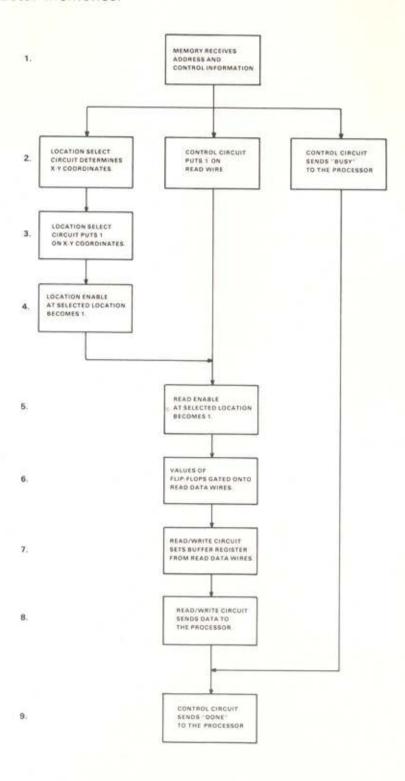

Figure 11 Read Memory Cycle (Semiconductor)

## Read Memory Cycle

The read memory cycle in semiconductor memory begins in the same manner as the read memory cycle for core memory.

- First, the memory receives from the processor the address of the memory location to be read and a read signal. The address is placed in the memory address register.

- Then, as the location select circuit decodes the contents of the memory address register to determine the X and Y coordinates, the control circuit puts a 1 on the read wire and sends a BUSY signal to the processor.

- After the location select circuit determines the X and Y coordinates that correspond to the referenced location, the selected X and Y lines are set to 1.

- This causes the location enable signal at the selected location to become 1 (X ANDed with Y).

- 5. The read enable line formed by ANDing the location enable and the read wire now becomes 1 . . .

- and the values of the flip-flops in the selected location are gated out onto the data-out ("read data") wires.

- 7. The read/write circuit reads the values of the "data-out" wires and sets the bits in the memory buffer register accordingly.

- Then the read/write circuit sends the data in the memory buffer register to the processor.

- Finally the control circuit sends the DONE signal to the processor, indicating that the memory is ready for another cycle.

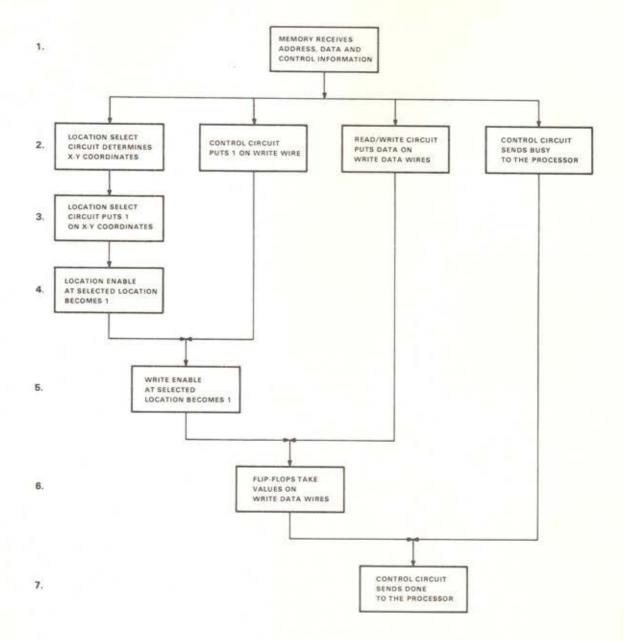

Figure 12 Write Memory Cycle (Semiconductor)

## Write Memory Cycle

The write memory cycle is also performed in one operation, i.e., one use of the X-Y coordinate wires.

- A write cycle begins when the memory receives the address of the memory location to be written into, the data to be written, and the control signal for a write. The address is placed in the memory address register and the data in the memory buffer register.

- Then, as the location select circuit uses the contents of the memory address register to determine the X and Y coordinates, the read/write circuit puts the contents of the buffer register on the data-in (write data) lines. Also, the control circuit puts a 1 on the write wire and sends BUSY to the processor.

- When the location select circuit determines the X and Y coordinates, it puts a 1 on the corresponding pair of X-Y coordinate wires.

- These two wires, ANDed together at the selected location, cause the location select signal at that location to go to 1.

- The location enable signal (1), ANDed with the write wire (1), causes the write enable signal to be a 1.

- When the write enable signal becomes a 1, the values on the data-in (write data) lines become the values of the flip-flops in the selected location, thus completing the write operation.

- 7. The control circuit then sends DONE to the processor thus indicating that the cycle is complete.

Note that each of these cycles only moves the data to or from the selected location. Data is not moved both ways in the same cycle as is the case with the 2-operation cycles of core memory.

## Metal-Oxide Semiconductor Memory (MOS)

The basic storage element in MOS memory is a cell with a circuit constructed of metal-oxide; hence, the name metal-oxide semi-conductor memory.

Flip-flops store the value of a bit as voltage and current. MOS storage cells use the presence or absence of electric charge to represent the value of a bit. The electric charge contained by MOS storage cells fades rapidly and must be refreshed periodically by performing read/write cycles approximately once every millisecond on each bit. These refreshing cycles are performed in the memory itself and do not involve the processor. Because of this required refresh cycle, MOS memory is often called dynamic, as opposed to static memory using flip-flops.

Recent developments in MOS technologies have incorporated flipflops as the storage element. To differentiate these from the other types of MOS memory, they are called *static MOS*. Although this type of MOS memory is slower than the dynamic kind, it requires no refresh cycles.

## Comparison of Core, Bipolar, and MOS Memories

The basic similarity between core and both bipolar and MOS semi-conductor memories is their function. Each is a high-speed internal storage device capable of storing hundreds of thousands of bits of information for convenient access by the central processor. Each of these memories uses a different medium to store information. Core, as you know, uses ferrite, doughnut-shaped rings mounted on a plane, which can be magnetized in one of two directions. Bipolar memory uses flip-flops contained in an integrated circuit chip and stores information, electrically, as voltage and current. MOS memories use storage cells contained in an integrated chip that stores information by the presence or absence of a charge within the cell.

Bipolar and MOS memories store data electronically. Therefore, they require only a single operation for read and write. Since the data is not changed in any way by a read, there is no need to restore the data as in core. This feature is called a *non-destructive read*. However, semi-conductor memories *are volatile*. Because they depend on electricity to store information, a loss of power can erase the contents of both bipolar and MOS memories.

MOS memory requires frequent *refreshing* to retain information. These refresh cycles are handled automatically within the MOS memory.

These three memory media can be compared in terms of access time (see Table 2). Access time, as you recall, is the interval of time required to find a specific storage location and either read data from that location or write new data into that location. Where core memory is involved, access time includes the restore time of the previous cycle.

Table 2 Comparison of Main Memory Media

|                   |              | Semiconductor            |                          |  |

|-------------------|--------------|--------------------------|--------------------------|--|

| Characteristic    | Core         | MOS                      | Bipolar                  |  |

| Storage element   | Ferrite core | Cell                     | Flip-flop                |  |

| Type of storage   | Magnetic     | Charge                   | Voltage/current          |  |

| Cycle time        | 900 ns       | 300-800 ns               | <300 ns                  |  |

| Cost per bit      | 0.3-0.5¢     | 0.3-0.8¢                 | 1-2¢                     |  |

| Power consumption | Low          | Medium                   | High                     |  |

| Volatility        | No           | Yes                      | Yes                      |  |

| Refresh cycle     | No           | Yes                      | No                       |  |

| Structure         | Core planes  | Integrated circuit chips | Integrated circuit chips |  |

Core requires at least 800 nanoseconds per cycle, while MOS completes a cycle in about 300 to 800 nanoseconds. Bipolar, the fastest of the three, requires less than 300 nanoseconds to complete a full memory cycle. In general, semiconductor memory is more than twice as fast as core memory.

Comparing core, bipolar, and MOS memories on the basis of cost per bit of storage reveals that the cost of core and MOS range from 0.3 to 0.8 cents per bit of storage capacity, while bipolar costs considerably more – from 1 to 2 cents per bit.

In terms of power consumption, bipolar memories are the largest consumers, about 10 times as much as MOS memory and 20 times more than core.

Although all three types of memory media are relatively compact, MOS memory is extremely dense. That is, thousands of bits can be stored on a single MOS memory integrated circuit chip. Bipolar memory requires slightly more chip area per bit than MOS, but it is still very compact.

- 6. Define the following terms as they refer to MOS memory:

- a. Refresh

- b. Dynamic

- c. Static

- 7. Fill in the blanks in the table below:

|                      |      |     | emiconductor |

|----------------------|------|-----|--------------|

| Characteristic       | Core | MOS | Bipolar      |

| Cycle time           |      |     |              |

| Power<br>consumption |      |     |              |

| /olatility           |      |     |              |

| Cost per bit         |      |     |              |

| Storage element      | i l  |     |              |

- 6. Define the following terms as they refer to MOS memory:

- a. Refresh The process of performing periodic read/write cycles on each MOS cell to replenish the charge that represents the information.

- b. Dynamic Dynamic is a characteristic of MOS memory which requires periodic read/write cycles to retain the information.

- c. Static A new type of MOS memory that uses flip-flops.

# 7. Fill in the blanks in the table below:

| Characteristic   | Core         | Sem        | iconductor |

|------------------|--------------|------------|------------|

| - indicatoristic | Core         | MOS        | Bipolar    |

| Cycle time       | 900 ns       | 300-800 ns | < 300 ns   |

| Power            |              |            |            |

| consumption      | Low          | Medium     | High       |

| Volatility       | No           | Yes        | Yes        |

| Cost per bit     | 0.3−0.5¢     | 0.3-0.8¢   | 1-2¢       |

| Storage element  | Ferrite core | Cell       | Flip-flop  |

| -  | - | ~ " | - |  |

|----|---|-----|---|--|

| EX |   | C 1 |   |  |

|    |   | ~ 1 | 9 |  |

8. Draw a flowchart that describes the steps of a read cycle for semiconductor memories. Draw a flowchart that describes the steps of a read cycle for semiconductor memories.

|   | - | V | - | D | 01 | C | _ | c |

|---|---|---|---|---|----|---|---|---|

| • | E | л | ᆮ | n | CI | 0 | ᆮ | J |

Draw a flowchart that describes the steps of a write cycle for semiconductor memories. Draw a flowchart that describes the steps of a write cycle for semiconductor memories.

# Improving Main Memory

## **OBJECTIVE**

Given four options for improving the performance of main memories, four definitions, and four reasons for use, be able to match each option with its definition and reason for use.

## SAMPLE TEST ITEM -

Four options for improving the performance of main memories, their definitions, and reasons for use are given below. Match each option with its definition and reason for use.

| Option                    | Definition | Reason for Use |

|---------------------------|------------|----------------|

| Cache Memory              |            |                |

| Memory Interleaving       |            |                |

| Read-Only Memory          |            |                |

| Auxiliary Power<br>Supply |            |                |

#### Definitions

- A device that provides electrical power to semiconductor memories when the external power fails.

- b. A memory whose contents cannot be written.

- c. A small semiconductor memory used in conjunction with core memory to hold the data from the most recent memory reference.

- d. A technique for overlapping core memory references to sequential memory locations by having sequential locations in alternate memory units.

## SAMPLE TEST ITEMS -

## Reasons for Use

- e. If power fails or the computer system malfunctions, the contents of the memory will not be destroyed.

- f. Allows processor to make another memory reference without waiting for core memory to complete the last half of its cycle.

- g. If power fails, contents of volatile semiconductor memory will not be lost.

- Speeds up memory references without the high cost and volatility of a completely semiconductor memory system.

Mark your place in the workbook and view Lesson 4 in the A/V program, "Main Memory."

As you have seen, there are negative characteristics inherent in both core and semiconductor memories. In terms of power requirements, cost, and reliability, core memory is very efficient. However, because of its 2-operation memory cycle, core usually requires twice the time of bipolar or MOS semiconductor memories to complete its cycle. Semiconductors are very fast (particularily bipolar) but are more expensive than core and, in addition, are volatile.

Modern technological advances in both core and semiconductor memories have compensated for some of these drawbacks and improved the performance of core and semiconductor memories. This lesson discusses options currently used to improve the performance of main memories.

## Interleaving

As you recall from our discussion of core memory, the read and write cycles each require two separate operations. The read cycle requires a restore operation to return the original data, and the write cycle necesitates setting the cores to zero before the writing can take place.

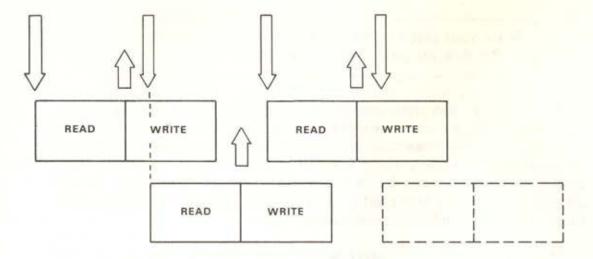

Obviously, both of these operations are time-consuming tasks. While the last half of a core memory cycle is being performed, the central processor is forced to wait. However, to make more efficient use of the processor, memory cycles can be overlapped with the use of two or more *independent* core memory units. This process, known as *interleaving*, is illustrated in Figure 13.

Interleaving involves alternating consecutive memory addresses between two separate core memory units. Specifically, all even addresses would select memory locations in one unit and all odd addresses would select locations in another unit. When this procedure is employed, both memory units operate simultaneously. Interleaving allows one memory cycle to begin before the previous memory cycle is completed.

Figure 13 Diagram of Interleaving

What this really means in terms of efficiency is that the processor can be executing a write operation from one memory unit while the other memory unit is still busy restoring a read operation. The processor might also be starting a read from one memory unit while the other unit is completing the write portion. In this way, the processor can continue to address sequential locations, although the actual memory locations are alternated between two separate core memory units.

Memory interleaving is accomplished by interchanging the least significant and the most significant bits contained in each memory address. This interchanging of address bits is done within the core memory units themselves and does not involve the central processor. In fact, memory interleaving is *transparent* to the processor. That is, the CPU continues to address core memory as if it were one continuous area of storage.

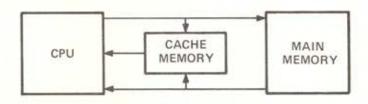

## Cache Memory

Another method used to improve the speed of core memory involves combining a small, additional, very high-speed semiconductor memory with the core memory This technique is called *cache memory* (pronounced "cash").

This small semiconductor memory stores the *most recent* information accessed by the processor. Each time the processor retrieves any information from the regular core memory, the cache memory copies it, replacing the oldest information contained in the cache memory.

The purpose of maintaining a cache memory is very simple. Very frequently, the central processor must reference the same memory locations many times. This procedure can be relatively slow when core alone is used. However, with cache memory, the information contained in those frequently referenced locations is all stored in the small, high-speed memory. Consequently, every time the processor needs that information, it can retrieve it rapidly from cache memory.

In systems that come with this configuration, the processor always checks the cache memory first before going to core. If the information required is not already written in the cache memory, it is written into the cache memory as the processor reads it from core. Eventually, when the information has not been used for a long time, it is replaced by more recent information. Thus, information is constantly being updated in the cache memory.

Figure 14 Cache Memory

By utilizing cache memory, information that is used over and over again can be accessed very rapidly. Since much of the information stored in main memory is needed many times, cache memory can represent a considerable increase in memory speed without the expense of a complete semiconductor memory system. It also eliminates the danger of lost information inherent in memories composed only of semiconductors. Cache memory provides an economical and efficient compromise between core and semiconductor memories for many computer applications.

## **Auxiliary Power Supply**

Since volatility is the most objectionable characteristic of semiconductor memories, a safeguard has been devised against the loss of power supplied to the memory. Battery-operated, auxiliary power supplies that automatically take over the power requirements of semiconductor memories when external power fails are connected to the memory unit. This battery-operated system functions until the external power is restored and prevents the loss of information.

## Read-Only Memory (ROM)

Semiconductor memory can be protected from accidental loss of information by using a read-only memory (ROM). Read-only memory differs from ordinary memory in that information is permanently written into a read-only memory and it cannot be changed or rewritten. Information stored in a read-only memory can be read as often as desired without changing or affecting the information in any way. Because the information contained in read-only memory is permanent, it is unaffected by loss of power or any malfunctions which occur anywhere in the computer system.

This type of memory is generally used in dedicated computers designed for a specific application. An ordinary read/write memory is used in addition to the read-only memory to store any variables required in the processing operation.

Read-only memories are also used in many computer systems to store the programs needed to start the computer when the power is first turned on.

This lesson introduced four techniques currently used to improve the efficiency of main memory. Advances in technology are continuously providing new solutions to the problem of optimizing the efficiency of this important unit of the digital computer.

| 1. | Th  | e primary weakness inherent in core memory rela<br>e):                                                                                              | ates to it | s (circle |

|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|

|    | a.  | Cost                                                                                                                                                |            |           |

|    | b.  | Speed                                                                                                                                               |            |           |

|    | C.  | Volatility                                                                                                                                          |            |           |

|    | d.  | Reliability                                                                                                                                         |            |           |

| 2. | Int | erleaving involves (circle one):                                                                                                                    |            |           |

|    | a.  | Using two different types of memories simultan                                                                                                      | eously.    |           |

|    | b.  | Using semiconductor memories.                                                                                                                       |            |           |

|    | C.  | Using two separate core memory units.                                                                                                               |            |           |

| 3. | De  | fine the term "transparent" with respect to inter                                                                                                   | leaving.   |           |

|    |     |                                                                                                                                                     |            |           |

|    |     |                                                                                                                                                     |            |           |

| 1  | Sn. | acify whether the following statements are two                                                                                                      | av falsa   |           |

| ٠. | Sp  | ecify whether the following statements are true                                                                                                     | T          | -         |

|    |     | Cooks manager (avaluate problem)                                                                                                                    |            | F         |

|    | a.  | Cache memory involves combining a small, high-speed semiconductor memory with a core memory.                                                        |            |           |

|    | b.  | A cache memory stores the oldest information accessed by the processor.                                                                             |            |           |

|    | C.  | Cache memory can improve the speed of the computer by allowing the processor to access more quickly information that is needed over and over again. | П          | П         |

|    |     | and and adding                                                                                                                                      |            |           |

| SO | LU | TI | ON | S |  |

|----|----|----|----|---|--|

|----|----|----|----|---|--|

| 1. Th | ne primary weakness inherent in core memory re                                                                                                      | lates to | its:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a.    | Cost                                                                                                                                                |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6     | Speed                                                                                                                                               |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |