#### **Chapter Meetings and Events**

SCV-EMS - 3/30 | Career Checkpoints and Introducing Technology to Make Everyday Devices See - check pointing your career, followed by time-of-flight 3D sensor chips for computer imaging, vision, distance measurement ... [more]

SCV-LEOS – 4/5 | Semiconductor Ultraviolet Optical Sources: Status, Challenges, and Applications - operation of AlGaInN materials system down to 340 nm and LEDs operating below 280 nm ... [more]

SCV-ED - 4/12 | VLSI Devices for Analog and Mixed-Signal App'ns carrier-tunneling studies in deep-submicron MOSFETs... [more]

SCV-EMC - 4/12 | EMI Analysis of complex systems; and Electrostatic Discharge - It failed! How to find the root cause different data analysis techniques; and ESD failure diagnosis ...

SCV-Comm - 4/13 | Where is the RFID Puck Going Next? - Wal-Mart, Target, Albertsons, , casinos, passports: where next? ... [more]

SCV-AP - 4/13 | A Spatial Channel Model for Multiple-Antenna Systems - assessing the optimal number of antennas for given transmit and receive areas ... [more]

SCV-EMB - 4/20 | Tactile Pressure Imaging: A New Tool For In Vivo Physiological Assessment for Gastroenterology - portable advanced pressure imaging system with high fidelity pressure maps of the gastrointestinal tract ... [more]

SCV-IM - 4/20 | ISO13485: A PDL and QSR Not Just for Medical Devices - a Product Development Lifecycle standard that can make the job of a product or program manager easier ... [more]

OEB-IAS - 4/21 | Electrical Power Generation, Distribution, and Plant Automation on Marine Vessels - systems have to be as specialized as the vessel to meet modern cargo demands ... [more]

OEB-Comm - 4/21 | Evolution of Mobile Wireless Technologies to the **Year 2008** - new products and services, and China's influence... [more]

SCV-SSC - 4/21 | Power-aware and Temperature-aware Circuit **Design** - max performance under power consumption constraints... [more]

SCV-PACE - 4/26 | **Resume-writing Clinic** - review the structure of a good resume, and bring your own for critique ... [more]

SCV-CNSV - 4/26 | Who Owns Your Brain? A Consultant's Guide to Patents - patents and intellectual property ... [more]

SCV-Rel - 4/27 | When to use HALT and when to use ALT predicting a wearout mechanism, with case studies ...

SCV-CPMT - 5/4 | US Electronics Industry Competitiveness in View of Globalization and Changing Technologies - IC and systems packaging: competitiveness of US industry ... [more]

SCV-CS - 5/7 | Sensor Networks - The New Environment - Saturday seminar, at Stanford ... [more]

#### **Upcoming Conferences in the Bay Area**

April 12-14: **IEEE Wescon**, Santa Clara Conv'n Ctr Exhibits, seminars, tutorials free admission [more]

May 7: SENSOR NETWORKS - The New **Environment**, held at Stanford Univ [more]

May 17-19: The Vision Show & Conference West, San Jose Convention Ctr – Exhibits, sessions [more]

May 23-25: Aeroacoustics Conference, Monterey Exhibits, seminars, tutorials [more]

May 24-26: Aircraft Noise and Emissions

**Reduction Symposium**, Monterey

plenary-track session, tutorial, mini-expo [more]

June 21-23: **POFWorld '05**. Santa Clara Conv'n Ctr Plastic Optical Fiber for Home and Auto – sessions, tutorials, exposition [more]

10/3-11/2: 9th Asilomar Conference on Signals, Systems, and Computers Call for Papers [more]

#### **Upcoming Courses:**

April 12: Motor Control ... Robot Manipulators ... Control System Design: A Review (three) [more] April 13: Designs for the High-Speed,

**Broadband Information Age** [more]

**April 13: Packaging Technology for**

**RF and RFID** [more]

April 12-13: Electromagnetic Compatibility **Tutorials (four)** [more]

April 25-29: Technology Review and Update [more]

5-day class, Naval Postgraduate School, Monterey May 4: SOP vs SiP vs SOC: Technology

**Directions for Systems Implementation**

Seminar featuring the technical staff at Georgia Tech [more]

**May 5: Influential Communication**

listening, filtering, speaking - at KLA-Tencor, San Jose [more]

May 21-22: Computational Aeroacoustics:

**Methods and Application** [more]

Support our advertisers

**Special Wescon Profile**

**pages 9-13**

MARKETPLACE – Services

page 3

**Conference Calendar**

page 30

[more]

## **IEEE GRID**

#### Your Networking Partner®

April 2005 • Volume 52 • Number 4

IEEE-SFBAC ©2005

Chairman Douglas B. Snow

Finance Chair James B. Lekas

Editorial Board Chair Jonathan B. David

> **OEB Director Annie Kong**

SF Director Julian Ajello

SCV Director **Ron Kane**

**ECI Directors**

**James Lamb James Hungerford Bernie Siegal**

SFBAC Manager **Marilyn Turner IEEE-SFBAC** 345 Forest Avenue Palo Alto, CA 94301 Tel: 650 327-6622 Fax: 650 321-9692 Email: ma.turner@ieee.org

IEEE GRID is the monthly newsmagazine of the San Francisco Bay Area Council of the Institute of Electrical and Electronics Engineers, Inc. As a medium for both news and opinion, the editorial objectives of IEEE GRID are to inform readers in a timely and objective manner of newsworthy IEEE activities taking place in and around the Bay Area; to publish the official calendar of events; to report on IEEE activities of a national and international scope; and to serve as a forum for comment on areas of concern to the engineering community by publishing contributed articles, invited editorials and letters to the editor.

IEEE GRID is published as the GRID Online Edition residing at www.e-GRID.net, and in a handly printable GRID.pdf edition, and also as the e-GRID sent by email twice each month to more than 24,000 Bay Area members.

Editor: Paul Wesling **IEEE GRID** 12250 Saraglen Dr. Saratoga CA 95070

Tel: 408 331-0114 / 510 500-0106 / 415 367-7323

Fax: 408 904-6997

Email: editor@e-grid.net

www.e-GRID.net

#### From the editor . . .

You're certainly aware by now that Wescon is at the Santa Clara Convention Center in April. We have a one-sheet "guide" to most of the free seminars, panels, and other events - see page 13 in this issue. You'll want to reserve your seat in one or more of the events during the 3-day run. And I'll plan to see you on the floor at Wescon!

I've found that a good way to find out what the new "hot buttons" are in our technologies is to scan the programs of upcoming conferences to see who is speaking and what the session and paper topics are. If it's an IEEE conference, and you're not able to attend, then the papers should soon be available in the IEEE XPLORE™ system. Why is this useful? Most of us work for a company, institution, or university that has "free" access to the full IEEE collection (over 1 million papers - actually, there are over 1,137,000 now). For those without corporate or institutional access, there is the Member Digital Library subscription, which gives you 25 papers each month - about as many as you'd want to read in a month!

You can get to IEEE's on-line database at ieeexplore.ieee.org; access to the index and to all abstracts is free to all. Select "Browse Conference Proceedings" and enter keywords or acronym from the event's title. you know that you can also find most of these papers by doing a search in Google?

While you're at the XPLORE website, sign up to receive an automatic email alert whenever one or more new issues of specific journals are posted. It's a free service.

Paul Wesling editor@e-grid.net

NOTE: This PDF version of the IEEE GRID - the **GRID.pdf** - is a monthly publication and is issued a few days before the first of the month. It is not updated after that. Please refer to the Online edition and Interactive Calendar for the latest information: www.e-GRID.net

#### Professional Services Marketplace – editor@e-GRID.net for information

#### Say you found them in our GRID MARKETPLACE

... than the **FINISH**TM

- PDQ Project Planning Workshop™

- Project Management Education

Jack Sivak 707.725.5628 jsivak@strategicprojectsystems.com

strategic ystems

#### Patent Agent

Jay Chesavage, PE MSEE Stanford 3833 Middlefield Road, Palo Alto 94303 patents(at)chesavage(dot)com

TEL: 650-494-9162 FAX: 650-494-3835

#### SHAX Engineering and Systems

**Electronics Design Services**

- Analog and Digital circuit design

- VHDL/Verilog coding and synthesis

- ASIC/FPGA from concept to production (650) 966-1835

ishakour@shax-eng.com www.shax-eng.com

#### Crystal Instruments

- DSP and Embedded System design

- Windows, WinCE, drivers, firmware

- High-speed, real-time, handheld

- Local support, low cost

sales@go-ci.com www.go-ci.com

#### Mixed-Signal IC Development

- From Inception to Production Transfer

- Turnkey, Design Services & Consulting

- Design Reviews & TroubleShooting

#### Mixel, Inc.

Excellence in Mixed Signal Design

(408) 274-2736

sales@mixl.com

www.mixl.com

**Publishing**: Books/e-books/articles for professionals by professionals

Training: Workshops equipping professionals for the global economy

Consulting: Improvements in operations/quality/customer education

#### Meridian Deployment CORPORATION

510-252-0878

www.mdc-learning.com publisher@meridiandeployment.com Serving the high-tech business communities

Wi-Fi, UWB, WBA, 3G, Bluetooth, Telematics, Satellites, DoD ... Wireless Systems

Contract R&D Technical consulting Antenna Design & development, RF/ Subsystem, Radio Frontend Integration,

Reference Designs, Concept to Products Contact Dr. Jamal S. Izadian ANTENNEM COMMUNICATION, LLC, 408-927-6880

info@antennem.com www.antennem.com

TEA

**Device Thermal Characterization** Package Thermal Characterization Thermal Test Boards Thermal Test Equipment & Fixtures

#### Bernie Siegal

Thermal Engineering Associates. Inc. 650-961-5900

info@thermengr.com www.thermengr.com

- Hardware and

- **FPGA Designs** PCB layout

- · Signal integrity analysis

- Reference designs for SOC companies

- Turnkey Product Development

408-321-8825 info@eDFXservices.com

#### (408) 472-3889 OPS ALACARTE info@opsalacarte.com www.opsalacarte.com

Professional Consulting Services to assist clients in developing and executing any elements of Reliability throughout the Organization and Product Life Cycle.

Goal Setting • MTBF Predictions • HALT • HASS/ESS •Assessments • FMECA • DVT/V&V • EOL Assessment •Program Plans • DoE • Rel Demos • Training/teaching •Gap Analysis • CAPA/CLCA • Life Tests ...and more

OPS ALACARTE pioneered Reliability Integration<sup>SM</sup> using muitiple tools together to increase the power and value of any Reliability Program.

### **Dr. James Zhuge** (650)-960-1188

GRID.pdf Do you provide a service? Would you like more inquiries? e-GRID

- Access 25,000 engineers and managers

- IEEE Members across the Bay Area

- Monthly and Annual Rates available

Visit our Marketplace (page 3)

Download Rates and Services information:

www.e-grid.net/docs/marketplace-flyer.pdf

#### **IEEE Professional Skills Courses**

#### new! Influential Communication

Date/Time: Tuesday, May 17, 8:30AM-4:30PM

Instructor: Barry Flicker

Location: at KLA-Tencor, San Jose -

Without a context of mutual value, trust and respect, techniques alone prove useless. This one-day course asks participants to evaluate their current communication environment according to these standards. We then begin to examine the three primary communication skills - clear goal setting, making our message audience-appropriate, and active/empathic listening - so that participants understand how to improve their working relationships in any situation. This is a highly experiential workshop applicable for people at every level of the organization.

#### **Session Objectives**

- Identify things that we may be doing or failing to do that contribute to difficult communication.

- Apply S.M.A.R.T. Criteria to set clear, mutually agreed upon objectives.

- Resolve questions of competence through effective application of the situational speaking model.

- Listen through difference to manage conflict and build influence.

Engineering Management & Components, Packaging and Manufacturing Technology Societies, SCV Chapters

#### **Key Topics**

- The Three Levels of Listening

- 8 Blocks to Effective Listening

- Clearing Listening Blocks

- How to Stop Defending

- Value Clarification: Out to Lunch Game

- Listening Through Differences

- How Values Filter What We Hear

- The Communication Triangle

- SMART criteria for Clear Communication

- Situational Speaking

Improve your skills – register for a skills class. Bring a team!

For complete information and registration form, see our Chapter website, right-hand column:

www.cpmt.org/scv/

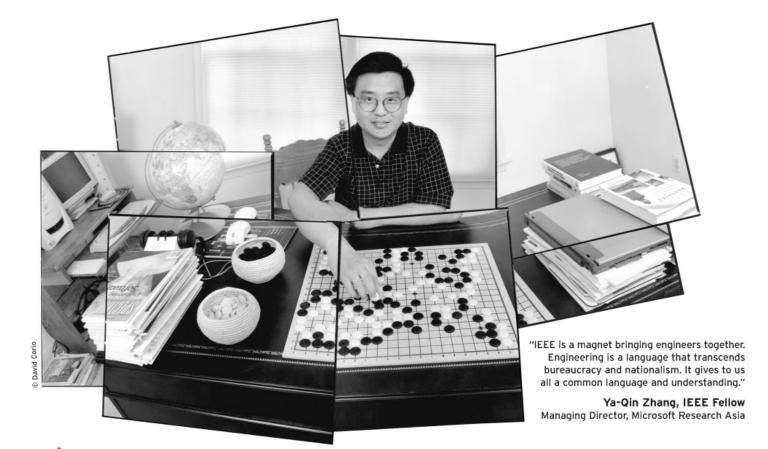

Build relationships in a worldwide community of innovators. Join IEEE.

APRIL 2005

**<b>∲IEEE**

Visit us at www.e-GRID.net

www.ieee.org/join

### 11th AIAA/CEAS Aeroacoustics Conference

23-25 May (Course: 21-22 May)

Co-located with the

## **AIAA/AAAF Aircraft Noise and Emissions Reduction Symposium**

24-26 May (Tutorial: 23 May)

**Hyatt Regency Monterey**

Held on the magnificent Monterey Peninsula

The 11<sup>th</sup> AIAA/CEAS Aeroacoustics Conference provides an international forum for scientists and engineers from industry, government, and universities to exchange knowledge and results of current studies and to discuss directions for future research. Papers that cover all aspects of the generation, propagation, measurement, modeling, and control of vehicle noise, as well as the effect of noise on structures and individuals, will be presented at the conference.

#### **KEYNOTE TALKS**

"Prospects for a Quiet Future in Aeronautics" Dr. Richard W. Wlezien, NASA

"Finding Hope Amidst the Challenges – Views of Aircraft Noise and Emissions Reduction"

John-Paul Clarke, MIT

#### **PROGRAM**

#### Over 30 sessions in 7 tracks, including:

- Acoustic/Fluid Dynamic Phenomena

- Airframe/High-Lift Noise

- Computational Aeroacoustics Methods

- General Acoustics

- Jet Noise Diagnostics

- Fan Noise Measurement and Modeling

- Jet Aeroacoustics Simulation

- Advanced Testing Techniques: Phased Arrays, Sensors and Methods, Facilities

- Community Noise and Metrics

#### TWO-DAY COURSE (Saturday, Sunday)

## Computational Aeroacoustics: Methods and Application

(fee includes full admission to Aeroacoustics Conference)

Computational issues unique to aeroacoustics - CAA

time marching algorithms - Radiation, inflow and

outflow boundary conditions - numerical solutions nonlinear wave propagation - multi-scales acoustics

- applications to aeroacoustics problems

The AIAA/AAAF

Aircraft Noise and

Emissions Reduction

**Symposium** is a high-level, multidisciplinary technical symposium bringing together leading engineers, scientists, researchers, government and civil aviation officials, industry, and policy makers to discuss the topics and issues of aircraft noise and emissions reduction. The objective is to review challenges and opportunities faced by manufacturers, local communities, air carriers, air navigation service providers, airports, governmental institutions, and non-governmental organizations to address noise and emission abatement and to develop holistic solutions that will ameliorate the pressures associated with air traffic growth.

#### PRE-SYMPOSIUM TUTORIAL

On Monday afternoon, Barry Scott, Director of the FAA Liaison Office, NASA Ames Research Center, will teach a course providing an overview of air traffic topics in preparation for discussions during the Symposium.

#### **PROGRAM**

The format of ANERS is a series of invited talks in a single-session, panel format and includes leading experts in the field. The program features balanced representation from Europe, the United States, and other regions of the world.

#### **MINI-EXPO**

There will be a Mini-Expo where organizations and manufacturers display information about their programs and products.

#### **REGISTER TODAY!**

Save \$100 – register by **April 22**. Special low student, retired rates!

For full information on both events:

www.e-grid.net/conf/aero-aners.html

### CALL FOR PAPERS

## Thirty-Ninth Annual Asilomar Conference on Signals, Systems, and Computers

#### Asilomar Hotel and Conference Grounds, Pacific Grove, California October 30 - November 2, 2005

**URL:** www.asilomarssc.org

Authors are invited to submit papers before June 1, 2005 in the following areas:

A. Communications Systems and Networking: 1. Error Detection and Correction, 2. Signal Representation and Spectral analysis, 3. CDMA, 4. Modulation and Detection, 5. Performance Bounds, 6. Synchronization, 7. Ultra Wideband, 8. OFDM / Multicarrier, 9. Networks, 10. Wireless Communications, 11. Optical Communications

**B. Adaptive Systems and Processing**: 1. Adaptive Filtering, 2. Adaptive Signal Processing, 3. Adaptive Beamforming, Adaptive Technologies for Communication, 4. Intelligent Hearing Aids

C. Array Processing and MIMO: 1. Array Processing,

- 2. Array Processing for Wireless Communications,

- 3. Sonar and Acoustical Array Processing, 4. Radar Array Processing, 5. MIMO / Space-time Coding

#### D. Biomedical Signal and Image Processing:

- 1. Medical Image Analysis, 2. Imaging Modalities,

- 3. Advances in Medical Imaging, 4. Biomedical Signal Processing, 5. Biomedical Applications, 6. Bioinformatics,

- 7. Image Registration and Multi-modal Imaging, 8. Image Reconstruction, 9. Computer Aided Diagnosis, 10. Functional Imaging, 11. Visualization

#### E. Signal Processing Algorithms and Applications:

1. DSP in Wireless Communications, 2. Radar and Sonar Signal Processing, 3. Energy Efficient DSP, 4. Low Rank Signal Processing, 5. Cooperative Analog / Digital Signal Processing, 6. Multimedia Signal Processing, 7. Multisensor / Multirate Signal Processing

**F. Architecture and Implementation**: 1. FPGA Implementation, 2. ASIC Implementation, 3. VLSI Implementation, 4. Computer Arithmetic, 5. Numerical Processing, 6. Architectures for Multimedia, 7. Security

#### G. Speech, Image and Video Processing:

1. Speech Processing, 2. Speech Coding, 3. Speech Recognition, 4. Narrowband / Wideband Speech and Audio Coding, 5. Document Processing, 6. Mathematical Models for Signal and Image Processing, 7. Image and Video Coding, 8. Image and Video Segmentation, 9. Image and Video Analysis, 10. Image / Video Security, Retrieval and Watermarking, 11. Image and Video Enhancement / Filtering, 12. Biometrics and Security

#### H. Tools and Strategies for Education

Prospective authors are invited to submit a 50 to 100 word abstract and an extended summary (500 to 1000 words, plus figures). Submissions must include the title of the paper, each author's name and affiliation, and the technical area(s) in which the paper falls with number(s) from the above list. Please visit the conference website ( www.asilomarssc.org ) for specific information on the electronic submission process. No more than <u>FOUR</u> submissions are allowed per contributor, as author or co-author. All submissions must be received by June 1, 2005. Notifications of acceptance will be mailed by late August 2005, and author information will be available on the conference website by mid September 2005. Full papers will be due at the conference and published in the spring of 2006. All technical questions should be directed to the Technical Program Chair, **Dr. Behnaam** Aazhang, e-mail: aaz@rice.edu, or the General Chair: **Dr. Hui Liu**, e-mail: hliu@ee.washington.edu.

#### **CONFERENCE COMMITTEE**

General Chair: Hui Liu, *University of Washington*Technical Program Chair: Behnaam Aazhang, *Rice University*

Conference Coordinator: Monique P. Fargues, Naval Postgraduate School

Publication Chair: Michael Matthews, Mission Research Corporation

Publicity Chair: Murali Tummala, Naval Postgraduate School

Finance Chair: Douglas J. Fouts, Naval Postgraduate School

The site for the 2005 Conference is at the Asilomar Conference Grounds, in Pacific Grove, CA. The grounds border the Pacific Ocean and are close to Monterey, Carmel, and the scenic Seventeen Mile Drive in Pebble Beach.

The Conference is organized in cooperation with the Naval Postgraduate School, Monterey, CA, Mission Research Corporation, Monterey, CA, and the IEEE Signal Processing Society.

## **The Vision Show and Conference** – West

May 17-19, 2005

## San Jose Convention Center Tutorials Sessions Exhibits

Machine vision solutions for many industries, including:

- Electronics

- Medical Devices

- Security

- Aerospace

- Automotive

- Lab Automation

- Semiconductors

- Pharmaceuticals

- Biometrics

- Food & Beverage

- Defense/Military

- Consumer Products

<u>The</u> Vision Show West is North America's leading showcase of machine vision components, systems and solutions. Held every other year in the heart of Silicon Valley, the Show is the perfect venue for suppliers and system integrators to meet with system designers and users to share information on new products and real-world solutions.

Morning and afternoon technical sessions include talks by Industry experts giving presentations designed specifically to provide practical, real-world solutions to attendees. Topics cover all key issues that current and potential users need to know in order to successfully apply machine vision.

#### Half-day Tutorials (Monday, May 16)

- How to Select Machine Vision Components

- Lighting & Optics: The Basics

- Integrating Machine Vision Systems: From Basic Concepts to Systems Integration

- Advanced Lighting & Optics

#### **Sessions** (Tues-Wed AM/PM, Thurs AM)

- Machine Vision Software for Part Identification/Classification

- Non-Visible Imaging

- Advances in Camera Technology

- Integrating a Machine Vision Solution into Capital Equipment

- Advances in Vision Guidance

- Advances in Smart Cameras and Sensors

- Successful and Emerging Machine Vision Applications

- Selecting the Right Camera Interface for Your Needs

- Latest Developments in Gigabit Ethernet for Machine Vision

- Advances in 3-D Machine Vision Technology

(For details on session papers, see the website)

#### Sponsored by the

#### Automated Imaging Association

#### **Exhibits**

The world's leading machine vision system and component suppliers will exhibit at **Vision West**, North America's largest and most targeted machine vision event. These are just some of the products you'll find:

- Complete Vision Systems

- Input/Output Devices

- Lighting Equipment

- Peripherals

- Vision Processors

- Cameras

- Frame Grabbers

- Lenses & Optics

- Smart Sensors

- Vision Software

#### **New Product Showcase**

Visit the **New Product Showcase** on our website to preview the newly introduced products that you can see at Vision West.

#### **Straight Talk on New Products**

In this special area right on the show floor, you'll hear presentations from technical experts at companies with new products on display, and get updates on important industry issues such as the Camera Link ⊕ and GigE Vision™ standards. These talks will run continually throughout the show — they're free to all show and conference attendees!

#### **Register Today**

**Free admission** to the three days of exhibits – register on the website!

With the **VISION SOLUTIONS PASS**, you can attend four days of in-depth tutorials and conference sessions for just \$765 (\$825 after April 20). You'll also receive a free copy of the conference proceedings CD and the tutorial handouts — great resources to take back to your company.

For information, and to register on-line:

#### www.machinevisiononline.org

Early-Bird Rates - Save through April 20th

To display at **Vision West**, contact Carol Calini at (203) 483-5774 or carol@reuterexpo.com

### **Technology Review and Update**

#### A Short Course for Technical Personnel and Decision Makers

Five Days – April 25 through April 29, 2005 Held at the Naval Postgraduate School, Monterey

This annual 5-day short course is designed for civilian, military, and government technical personnel and decision makers interested in refreshing and updating their knowledge in important technical areas. The success and popularity of this short course is ensured through recruiting of outstanding experts from industry, academia and the government and by constantly fine tuning the contents. It provides an excellent overview and stresses the more practical aspects of the topics discussed.

#### **TOPICAL AREAS:**

- Internet Security Opportunity or Oxymoron

- Integrated Circuits

- Information Systems, Operations and Strategies

- Microelectromechanical Systems (MEMS) An Introduction and 5-Year Vision

- Electro-Optical and Infrared Systems

- Bioengineering and Biotechnology

- Military Satellite Communications Technology

- Commercial Satellite Communication Technologies and Trends

- Tour of Selected NPS Laboratories

- Space Systems Laboratories

- Fiber-optics Laboratory

- Radar and EW Laboratory

- Virtual Reality Laboratory

Hosted by: The Naval Postgraduate School, Monterey

Cost: \$800 (checks only, no credit cards) Includes all

sessions, tours, and Wednesday dinner

Registration: Trinh Hoang, 831-656-2958 nthoang@nps.navy.mil

#### Register on-line through April 20!

For full schedule, module outlines, and instructors, download the Course Flyer at:

www.e-grid.net/docs/trau.pdf (PDF, 50 kB)

Further information and on-line registration:

www.sp.nps.navy.mil/trau/

IEEE Computer Society, SCV Chapter, and the North America Taiwanese Engineers' Association

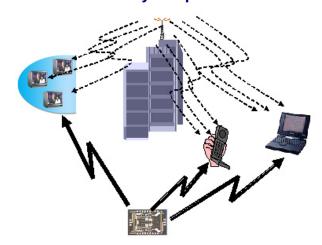

## SENSOR NETWORKS — The New Environment 7th IEEE/NATEA Annual Conference

Place: Braun Auditorium, Stanford University

Date: Saturday, May 7th, 2005

This one-day conference focuses on emerging Sensor Networks technologies. Sensor Networks move computing from being a distinct entity within an environment to becoming a seamless part of the environment. This profound change touches both computing and the way we operate daily life. Sensor Networks technologies they represent are fast becoming a new reality. In order to better understand this technology emerging and its complex present interactions. we this one-day conference on Sensor Networks. Starting with the hardware, this conference will cover such vital issues as wireless networking, distributed algorithms and applications at the engineering level. The aim of this conference offering is to members of the engineering communities with enough basic information to be able to make decisions regarding sensor networks and their applicability in new and emerging technical environments.

#### Program:

- Keynote: Sensor Network Overview

- Hardware Design in Integration of Sensor Networks

- Wireless Networking

- Distributed Algorithms

- System Design including Transceivers, Transmitters and Receivers

- Applications of Sensor Networks

#### **REGISTER TODAY!**

Rregister early to ensure a seat for this technical program.

| REGISTRATION       | STRATION By April 30 |         |

|--------------------|----------------------|---------|

| IEEE MEMBER        | \$50.00              | \$60.00 |

| NON-MEMBER         | \$60.00              | \$70.00 |

| STUDENT (fulltime) | \$25.00              | \$30.00 |

| UNEMPLOYED*        | \$25.00              | \$30.00 |

Registration includes lunch. More information and PayPal payments:

www.natea.org/NFIC/

# APRIL 12-14 Santa Clara Convention Center D2M: Design to Manufacture Solutions

#### Welcome to the exciting world of Wescon, and its new location in the Santa Clara Valley.

Wescon is the re-engineered industry event for the total design-to-manufacture process. The Wescon/2005 Exhibit and Conference Program broadens its focus to the needs of the design, systems, production, and support engineer to bring new visions of where technology is taking us, today and tomorrow.

Wescon brings engineers and scientists together in an environment that advances their education and careers by opening doors to a wealth of intellectual property, a wide range of technology tools and components, and access to immediate solutions for commercial applications.

#### Keynote:

#### Is the Wireless Industry Disconnected?

Martin Cooper, Array Communications

Special Sessions (free):

#### **Spintronics: A New Spin on Electronics**

Kevin Roche, Staff Engineer/Scientist, IBM Almaden

#### **Advances in Wireless Communications**

Dr. Arthur W. Astrin, Senior VP, STEP Communications

Mark your Calendar now!

Wescon – owned by engineers and run by engineers to benefit engineers.

#### **Test & Measurement Track**

**Free** Tutorials and Panels:

**Advances in Signal Integrity Testing**

Rick Nelson, Editor in Chief, Test & Measurement World

Testing and Troubleshooting Serial Data Signals and Getting More Out of Your Digital Oscilloscope

Dr. Michael Lauterbach, LeCroy Corporation

Productivity Features in Mid-range, Windows Oscilloscopes Bill Leineweber, Tektronix Debugging Elusive Digital System Problems Using Sophisticated Logic Analyzer Triggering and Faster Ways to Characterize Transients RF Signals

David Hayworth, Tektronix

Test Data Management System Optimizes Product

Development Process Don Holley, VI Technology

High Speed Probing and Signal Fidelity

Roland Crop, Tektronix

#### Design & Analysis Track

To deal with increasing chip- and system-level complexity, designers depend on a variety of design and analysis tools to successfully develop their products from conception through the manufacturing supply chain.

**Free** Tutorials and Panels:

Innovative Approaches to Tackling the Challenges of **D2M** Steve Schulz, President and CEO, Si2

Morning session topics: – DFM: The Physics – Yield: The Basics – Lithography Challenge – Design Optimization Yield – Test to Yield Prediction – Design for Yield: Mixed Signal Analog – Library Challenge

Meeting the Challenges of Complex Systems Design Henry Potts, Vice President and GM, Mentor Graphics

**Advanced Interconnect** David Wiens, Mentor Graphics *Also*:

**Cost Trade-offs and Design Techniques for Embedded Passives and HDI Technologies**

**Integrated Systems Design -- Trends, Challenges** and Solutions

#### Register for free pass and events today:

www.wescon.com

Continued, next page

#### Tutorials and Seminars co-located at WESCON in Santa Clara – April 12-14

SCV Microwave Theory & Techniques Chapter

### Designs for the High-Speed, Broadband Information Age

- Wednesday, April 13, 2005

- Seminar: 8:30 AM Noon

- Registration/Breakfast: 8 AM 8:30 AM

- Santa Clara Convention Center

- In conjunction with IEEE WESCON'05

- Includes free admission to WESCON exhibits

More information on Page 10

SCV Control Systems Chapter

#### **Three Seminars**

(choose one, or all three)

**General Concepts of Motor Control**

8:30 AM – 11:00 AM

**Understanding Robot Manipulators**

11:30 AM – 2:00 PM (includes lunch)

**Control System Design: A Review**

2:30 PM - 5 PM

- Wednesday, April 13, 2005

- Santa Clara Convention Center

- In conjunction with IEEE WESCON'05

More information at

www.ewh.ieee.org/r6/scv/css/

SCV Components, Packaging & Mfg Technology Chapter

## Packaging Technology for RF & RFID

- Wednesday, April 13, 2005

- Seminar: 1:00 5:30 PM

- Registration: begins at Noon

- Santa Clara Convention Center

- In conjunction with IEEE WESCON'05

- Includes free admission to WESCON exhibits

- Plenty of free parking

With the advent of RFID chips in the commercial sphere, many companies and individuals are taking an interest in this emerging market. Major retail outlets as well as government uses of the devices are spurring a great deal of speculation about the future of the technology and creating demands for lower cost. Because of the small size and extreme cost constraints, packaging and test of these unique devices presents a challenge in terms of handling, yield and cost. This seminar will bring together leading experts in the field to discuss manufacturing, infrastructure, packaging and cost reduction efforts in the industry. The seminar also addresses packaging trends for RF subsystems and systems, with a focus on the latest in System-in-Package technology. (see also the "SoP/SiP/SOC" Seminar on May 4.)

The topics include:

- · RFID technology and deployment

- Packaging technology and standards

- Manufacturing and cost considerations

- Training opportunities and sources of more information

#### **PROGRAM**

Introduction and Overview – Seminar Chairman

- Al Scott Besser Associates "Overview of RFID Technology and Deployment"

- Raj Bridgelall Alien Technology "Packaging Technology for UHF RFID Tags"

- Prof. Vivek Subramanian, UC-Berkeley "

Prospects for all-printed RFID: Technology,

Opportunities, and Challenges"

- Telesphor Kamgaing, Intel Corporation –

"Design of Small-Form-Factor RF packaging for Wireless Communication Systems "

- Norm Owens, Freescale Semiconductor "RF/Microwave Packaging Technology at Freescale Semiconductor"

#### **REGISTER TODAY!**

The seminar is filling up fast, so register early to ensure a seat for this interesting technical program.

| REGISTRATION       | By April 1 | After April 1 |

|--------------------|------------|---------------|

| IEEE MEMBER        | \$75.00    | \$95.00       |

| NON-MEMBER         | \$110.00   | \$125.00      |

| STUDENT (fulltime) | \$30.00    | \$35.00       |

| UNEMPLOYED*        | \$30.00    | \$35.00       |

\*With proof of unemployment

Regiser through PayPal or use registration form:

www.cpmt.org/scv/courses/rfid.html

#### Tutorials and Seminars co-located at WESCON in Santa Clara – April 12-14

## **Explore Wescon at**

www.wescon.com

SCV Electromagnetic Compatibility Chapter

Four Half-Day Tutorials (choose one, or all four)

Fundamentals of Electromagnetic Compatibility

April 12 – 8:00am – noon

Fundamental Concepts of Signal Integrity & EMC Related to Printed Circuit Boards

April 12 – 1:00pm – 5:00pm

Testing for EMC Compliance – Approaches and Techniques

April 13 - 8:00am - noon

Fundamentals of Grounding and Shielding for System Level Noise Reduction

April 13 - 1:00pm-5:00pm

**Instructor: Mark Montrose**

Montrose Compliance Services, Inc.

#### Other Tutorials:

Key Issues of EMI/EMC

April 14 – 9:00am – Noon

High-Frequency Digital Design and PCB Layout

April 14 – 1:00pm – 4:00pm

Get full information and register at

www.wescon.com

#### **Exhibits**

Discover innovative design tools, test equipment, services and component-level products for the next generation of electronic systems. Products that include:

- Design and Analysis

- Test and Measurement

- Prototype Production

- Power Components

- Active, Passive & Electro-mechanical Components

- Interconnects

Two-one-day seminars (no cost)

Designing low cost systems using Xilinx Spartan-3 Generation FPGAs

April 12 - Low Cost DSP Systems

**April 13 - Low Cost Embedded Processing Systems**

Register though the Wescon website

#### **Industry Leaders**

Respected leadership from across industry sectors join together to determine IEEE Wescon's content and direction. The Advisory Committee for this spring's event includes:

**Dr. Meyya Meyyappan**, Director, Center for Nanotechology, NASA Ames Research Center

Larry Tracewell, President and CEO, Tracewell Systems Dr. Jack Pearson. Former Vice President and General

Manager, Air Combat and Strike Systems, Raytheon

Masami Yamamoto, Co-founder and Chairman, Beganto, Inc. Mark Strauch, Deputy Program Director, Engineering,

Lawrence Livermore National Laboratory

**Dr. Anthony F. Laviano**, Council on Nanotechology, National Academy of Science

**Bernie Siegal**, IEEE Fellow & Director, Thermal Engineering Associates, Inc.

## Designs for the High-Speed, Broadband Information Age

Wednesday, April 13, 2005Seminar: 8:30 AM – Noon

Registration/Breakfast: 8 AM – 8:30 AM

Santa Clara Convention Center

• In conjunction with IEEE WESCON'05

Includes free admission to WESCON exhibits

Plenty of free parking

As the need for higher data rates and faster user interfaces increases, demands are placed on both the technology used to transmit and receive this information and on its designs. Previously, the realm of high speed, high frequency, high bandwidth circuits was relegated to III-IV materials like GaAs or InP. Recently, advances in materials like Si and SiGe have forced designers to look at these technologies to keep the cost low and to be competitive. Additionally, innovations like those in newer materials like GaN have been sought to provide advantages for these types of circuits.

Therefore, the ability to understand how the requirement for higher speed and faster data rates drives microwave circuit designs and the ability to design circuits in these various technology choices is an important part of the contemporary engineer's job as well as his/her value to an organization. The main challenges for today's microwave circuit designer are to understand which technology to use for a given application and know the tradeoffs and limits when designing in these technologies.

This seminar will explore the advances that have been made in these various material technologies and their affect on IC designs. Speakers will cover:

- The applications and requirements for higher speed and faster data rates

- The advantages and disadvantages of these technologies for handling higher speed/data rate applications

- How the need for faster and increased quantity of information affects circuit designs

- Current examples of designs and the tradeoffs addressed

To register, send your contact information and the fee to: Benson Chan (MTT Treasurer)

M/A-Com 5300 Hellyer Ave

San Jose, CA 95138

Phone# 408-624-3359

## Microwave Theory & Techniques Society Santa Clara Valley Chapter

#### **PROGRAM**

## **100GHz CMOS Circuits and the High Speed Broadband Information Age**

Dr. Luiz Franca-Neto, Technical Leader and Manager, Broadband Wireless Division (BWD) Intel Communications Group (ICG), Intel Corporation

## **SiGe and RFCMOS Technology for the High Speed Information Age**

Dr. Xiaojuen (Ben) Yuan, Ph.D, IEEE Senior Member, Vice Chair, SSC/AP/MTT IEEE San Diego Chapter, IBM West Coast Foundry Applications

#### InP HBT Design for 100 to 200GHz IC's

Dr. Zachary Griffiths, Post Doc Researcher, UC Santa Barbara

## SiC and GaN Based Transistor and Circuit Advances Mr Simon Wood Principal RF Design Engineer,

Cree Microwave

#### **REGISTER TODAY!**

Space is limited, so please mail in your registration before **April 9**. Registration fee includes breakfast and the course CD (proceedings).

| Registration Fee:   | Pre-Reg'n by <b>Apr 9</b> | After Apr 9 |

|---------------------|---------------------------|-------------|

| <b>IEEE Members</b> | \$50                      | \$65        |

| Nonmembers          | \$75                      | \$90        |

| Students            | \$30                      | \$30        |

| Unemployed *        | \$30                      | \$30        |

|                     |                           |             |

\* Bring or send a photocopy of unemployment check receipt dated within 2 weeks of registration to qualify

For Workshop registration information, please visit the MTT Chapter website:

www.mtt-scv.org

#### **IEEE**

## Wescon

Connecting Engineers, Business and Technology

April 12–14, 2005 Santa Clara Convention Center NO CHARGE For All Events Listed Below. (Please circulate)

Complete conference information available at <a href="https://www.wescon.com">www.wescon.com</a>

Seminar/Course Info: www.e-grid.net/docs/wescon05.pdf

Priority Code: GRID

#### Express Registration — for Exhibit Floor and Complimentary Conference Events

| Name             | _Title  |

|------------------|---------|

| Company          | Address |

| City, State, Zip | Email:  |

#### Please check each event you plan on attending (all at No Charge)

| T lease check each event you plan on attending (an at 140 Charge)               |                                                                      |               |                 |           |   |  |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------|-----------------|-----------|---|--|

| IDEB                                                                            | Wescon Exhibit Hours                                                 | 10-5          | 10-5            | 10-4      |   |  |

|                                                                                 |                                                                      | Tue 4/12      | Wed 4/13        | Thu 4/14  | ļ |  |

| TEED                                                                            | IEEE Wescon Conference Hours 8:00-5:30                               |               | 8:00-5:30       | 9:00-4:00 |   |  |

| Tuesd                                                                           | lay, April 12                                                        |               |                 | V         |   |  |

| P1                                                                              | Panel - Advances in Signal Integrity Testing                         |               | 10:00am-11:30am |           |   |  |

| SS1                                                                             | Spintronics: A New Spin on Electronics                               |               | 1:00pm-2:30pm   |           |   |  |

| T1                                                                              | Testing and Troubleshooting Serial Data Signals                      |               | 1:30pm-3:00pm   |           |   |  |

| T2                                                                              | Productivity Features in Mid-Range, Windows Oscilloscopes            |               | 3:30pm-5:30pm   |           |   |  |

| Wedn                                                                            | nesday, April 13                                                     |               | 1               |           |   |  |

| K3                                                                              |                                                                      |               | 8:00am-8:45am   |           |   |  |

| SD4 Design for Manufacturing Fundamentals                                       |                                                                      | 8:45am-9:15am |                 |           |   |  |

| SD5                                                                             | Design for Yield Fundamentals                                        |               | 9:15am-9:4      | 5am       |   |  |

| SD6                                                                             | Optical Lithography Foreverand DFM, The Good, The Bad and The Ugly   |               | 9:45am-10:1     | 5am       |   |  |

| T3                                                                              | Getting More Out of Your Digital Oscilloscope                        |               | 10:00am-11:     | 30am      |   |  |

| SD7                                                                             | Design for Manufacturability in an Analog World                      |               | 10:15am-10:     | 45am      |   |  |

| SD8                                                                             | Design Optimization for Yield                                        |               | 10:45am-11:     | 15am      |   |  |

| SD9                                                                             | Redefining Test for the DFM Era                                      |               | 11:15am-11:     | 45am      |   |  |

| SD10                                                                            | Library Challenges                                                   |               | 11:45am-12:     | 15pm      |   |  |

| K1                                                                              | Keynote - Meeting the Challenges of Complex Systems Design           |               | 1:00pm-1:50pm   |           |   |  |

| T4 Debugging Elusive Digital System Problems Using Sophisticated Logic Analyzer |                                                                      | 1:00pm-2:30pm |                 |           |   |  |

| P2                                                                              | Panel - Coming Issues and Innovation                                 |               | 2:00pm-3:3      | 0pm       |   |  |

| SD1 High Speed Design – Not Just Simulation; a Process                          |                                                                      | 2:00pm-2:45pm |                 |           |   |  |

| SD2 Cost Trade-Offs and Design Techniques for Embedded Passives and HDI         |                                                                      | 2:45pm-3:30pm |                 |           |   |  |

| T5                                                                              | T5 Faster Ways to Characterize Transient RF Signals                  |               | 3:00pm-4:30pm   |           |   |  |

| T5 Faster Ways to Characterize Transient RF Signals                             |                                                                      | 3:00pm-4:30pm |                 |           |   |  |

| SD3                                                                             | SD3 Integrated Systems Design – Trends, Challenges and Solutions     |               | 3:45pm-4:30pm   |           |   |  |

| P3                                                                              | P3 Panel - Integrated Systems Design Panel Discussion                |               | 4:30pm-5:30pm   |           |   |  |

|                                                                                 | sday, April 14                                                       |               |                 |           |   |  |

| S1                                                                              | Frequency Control Technical Seminar                                  |               | 9:00am-10:15am  |           |   |  |

| K2                                                                              | 2 Keynote - Is the Wireless Industry Disconnected?                   |               | 10:00am-11:30am |           |   |  |

| T6                                                                              | T6 Test Data Management System Optimizes Product Development Process |               | 10:00am-11:30am |           |   |  |

| T7 High Speed Probing and Signal Fidelity                                       |                                                                      | 1:00pm-2:30pm |                 |           |   |  |

| SS2                                                                             | SS2 Advances in Wireless Communications                              |               | 1:00pm-2:30pm   |           |   |  |

PRIOR TO FRIDAY, APRIL 8 - Fax to 310-410-0164. AFTER April 8, Bring form to IEEE Wescon

Santa Clara Convention Center Plenty of Free Parking

#### "SOP vs SiP vs SOC: Technology Directions for Systems Implementation"

**Emerging and Disruptive Packaging Technologies for the Next Decade**

Featuring the technical staff of the NSF-sponsored Georgia Tech Packaging Research Center

Held at the Ramada Inn, Sunnyvale Wednesday, May 4, 2005, from 8:00 AM - 5:30 PM

System-on-Package (SOP) refers to ultra-miniaturization of systems using thin-film component integration, in contrast to transistor integration for ICs. This provides a "Moore's Law" for system integration, akin to Moore's Law for IC integration. The SOP paradigm changes the current chip-centric System-on-Chip (SOC) methodology to a cheaper, faster-to-market IC-package-system co-design flow. The advantages of the SOP paradigm over SOC appear overwhelming due to SOPs design simplicity, lower cost and higher system functional integration, improved electrical performance, and without the intellectual property issues that dominate SOC. SOP is also different from and offers advantages over 3D packaging and SIP. The 3D packaging is a general concept for stacking of similar or dissimilar chips (such as DRAMS or DRAMs) with processor and flash memory. The SIP can go beyond, to embed both active and passive devices. The SOP focuses on integrating heterogeneous system functions, optimizing the integration of digital, RF, optical, sensor and other technologies.

#### **DATE & TIME:**

• Wednesday, May 4, 2005, from 8:00 AM - 5:00 PM

Registration: 7:30 AMLunch: Noon - 1:15 PM

• Reception/dinner following: 5 - 8 PM (optional)

#### COST:

IEEE Members: \$95 Non-Members: \$150

• After April 25: Member \$110, Non-Member \$165

• Includes lunch, class booklet, refreshments, and admission to the optional evening reception

#### WHO SHOULD ATTEND:

Packaging engineers, photonics engineers, systems engineers, thermal and mechanical engineers, PCB layout engineers, design, process, failure analysis, and reliability engineers and managers.

#### **PROGRAM:**

Morning Session (8:00-11:45 AM)

"SOP: The Second Moore's Law for Systems in

Contrast to First Moore's Law for ICs," Prof. Rao

Tummala, Director, GaTech Packaging Research Center

"Mixed Signal SOP Design," Prof. Madhavan

Swaminathan

High-Density/High-Throughput Chip-to-chip Optical Interconnect SOP for Next-Generation Computing and Communication Systems," Prof. Gee-Kung Chang "RF/Wireless 3D Packaging and Integration: Current Challenges and Solutions," Prof. Manos Tentzeris

**Lunch Session** (12:00-1:15 PM – includes Buffet Lunch) Keynote Presentation: "**US and Electronic Industry Competitiveness in view of Globalization and Changing Technologies**," Prof. Rao Tummala

Afternoon Session (1:30-5:00 PM)

"High Performance Nano Materials for Electronic,

Photonic and MEMS Packaging," Prof. C.P. Wong

"Multigigahertz Test Methods for SOPs and Waferlevel Packaged Devices," Prof. David Keezer

"Thermo-Mechanical Reliability and Design Challenges

for Next-Generation Microsystems Packaging," Prof.

Suresh Sitaraman

Evening Session (5:00-8:00PM – optional)

Informal Reception and Social with Drinks and Light

Dinner. Meet the Georgia Tech PRC faculty members for informal discussions

For Seminar registration information, please visit the Chapter website:

www.cpmt.org/scv

Use our PayPal registration and payment system online

## **TUESDAY MARCH 29**

## Origin of Tunneling Spin Polarization

Speaker: Dr. Stuart Parkin, Director, IBM-Stanford

Spintronic Science & Applications Center,

IBM Almaden Research Center

Time: Coffee and conversation at 7:30 p.m.

Presentation at 8:00

Place: Komag, 1710 Automation Parkway,

San Jose not required

RSVP:

Web: www.e-grid.net/docs/0503-scv-mag.pdf

**Stuart Parkin** joined IBM Research in San Jose in 1982 as a post-doctoral Fellow, becoming a permanent member of the staff the next year. Dr. Parkin's research interests have included organic superconductors, high-temperature superconductors and, most recently, magnetic thin-film structures and spintronic materials and devices for advanced sensor, memory and logic applications.

In 1991, Dr. Parkin discovered oscillations in the magnitude of the interlayer exchange coupling in magnetic multilayered systems transition-metal exhibiting giant magnetoresistance (GMR). development led to the creation of GMR sensors that enabled huge increases in hard-disk drive data density. For this and related work, Dr. Parkin shared the American Physical Society's International New Materials Prize (1994) and the European Physical Society's Hewlett- Packard Europhysics Prize (1997). He is a Fellow of the Royal Society, the American Physical Society, the Institute of Physics (London), the Institute of Electrical and Electronics Engineers and the American Association for the Advancement of Science. In 1999 he became an IBM Fellow, IBM's highest technical honor. Dr. Parkin has authored more than 300 published papers and has 47 issued U.S. patents.

Dr. Parkin received his B.A. degree (1977) and was elected a Research Fellow (1979) at Trinity College in Cambridge, England, and earned his Ph.D degree (1980) at the Cavendish Laboratory, also in Cambridge. Since 1997 Dr. Parkin has been a Consulting Professor in the Department of Applied Physics at Stanford University. He is also Director of the IBM-Stanford Spintronic Science and Applications Center, which was formed in April 2004

The relationship of the spin polarization of current tunneling from a ferromagnetic material (through a tunnel barrier) to its magnetization is of considerable current interest, particularly with regard to the development of magnetic tunnel junctions with high tunneling magnetoresistance suitable for magnetic memory and sensor applications1. The tunneling spin polarization (TSP) can be directly measured using superconducting tunneling spectroscopy (STS) inferred from measurements of tunneling magnetoresistance (TMR). The TSP depends not only on the ferromagnetic material but also on the tunneling barrier. Using crystalline (100) oriented MgO tunnel barriers and bcc CoFe electrodes, TSP

values exceeding 85% are found from STS studies at 0.25 K with TMR values greater than 300% at 5K2. The same ferromagnetic electrodes using conventional amorphous alumina barriers exhibit TSP values of only ~50%. In these cases the **TSP** sign of is positive corresponding to the preferential tunnelina maiority of

However, using magnetic electrodes electrons. formed from the ferrimagnetic rare-earth transitionmetal alloys, such as Co-Gd, we show that the sign of the TSP and TMR can be either positive or negative depending on the composition of the alloy and temperature. For alloys of Co and Fe with Pt and Pd we show that the TSP is strongly influenced by bonding at the tunnel barrier/ ferromagnetic electrode interface. In particular, we compare results for CoPt alloys with AIN and AI2O3 tunnel barriers. For AIN barriers the TSP decreases linearly with increasing Pt content whereas for Al2O3 tunnel barriers the TSP has only a weak dependence on Pt content for up to ~50 atomic % Pt. These results can be understood as a consequence of stronger Co - oxygen bonds as compared to Pt – oxygen bonds.

### SCV Engineering Management

## **WEDNESDAY MARCH 30**

#### Forum: Career Checkpoints

Speaker: Robyn Chew-Gibbs, HR Training & Development Manager, Juniper Networks

and

## Introducing Technology to Make Everyday Devices See

Speaker: Dr. Abbas Rafii, Executive VP,

Canesta, Inc.

Time: Forum at 6:00 PM, Dinner at 7:00 PM,

after-dinner presentation at 7:45 PM

Place: Prime Hotel, 1300 Chesapeake Terrace,

Sunnyvale - off Lawrence Expy/Caribbean

Dr at Hwy 237

RSVP: Please reserve in advance through website

Web: www.ieee-scv-ems.org

**Robyn Chew-Gibbs**, Human Resources Training & Development Manager at Juniper Networks, will lead the group through a working session designed to show how to productively analyze and plan your career direction.

In September of 2004, Robyn joined Juniper Networks as the first Human Resources Training Manager. Responsible for management development and "soft skills" training world wide, Robyn continues to be motivated by the excitement that employees exude when mastering a new skill that results in personal growth and positive business impacts!

Formerly, she was employed for 9 years at Levi Strauss & Co. She was part of the Corporate Training & Development department where she facilitated various training programs including Performance Management, Valuing Diversity and Leadership training. During her tenure at Levi's she was tapped by the CEO to direct the Corporate Work/Family Initiative. This initiative, one of the few of its kind at the time, earned Levi's recognition by Working Mother magazine as one of the "Top 100 Companies for Women."

After achieving her goals at Levi's, Robyn began her own consulting firm, specializing in management and employee development. During the 10 years as a consultant, she amassed a loyal clientele including Wells Fargo Bank, Advanced Fibre Communications, Blue Shield of California, Industrial Light + Magic, (continued, next column)

#### Career Checkpoints (before-dinner Forum)

The speed of change causes many to ask: "Where will I be in x years"? The better question is: "Where will I be next year?" Taking it one step further, the ideal question is: "Where do I want to be next year?"

How often have you said, "I wish I could change jobs or change careers!" Chances are this question will remain rhetorical until you closely examine the reasons you state this wish and begin to uncover what is at the root of your desire for change. Once understood, creating an appropriate plan becomes an easier & more successful undertaking.

## Introducing Technology to Make Everyday Devices See (After-Dinner presentation)

Despite impressive advances in imaging technology, computers remain essentially blind and unable to make sense of their environment. The advances in time-of-flight 3D sensor chips promise to bring this technology to large volume deployment, making ranging the next big development in computer imaging and vision markets. Canesta's work in this area enables everyday devices to recognize and intelligently interact with their environments. Bringing the technology to the market involved making many challenging technical and business decisions.

(continued)

Skywalker Sound, Intel and Oracle. Robyn holds certifications in Myers Briggs Type Indicator and Project Management.

Robyn is a native San Franciscan and 3rd generation Chinese-American. She earned Undergraduate and Graduate degrees from the University of California at Los Angeles.

**Dr. Abbas Rafii** is Executive Vice President and one of the founders of Canesta, Inc. He has extensive background in software engineering and business management. His current focus is directing the software development for the company's Electronic Perception Technology. Earlier, he directed the development of Projection Keyboard application. He received his MS and Ph.D. in EECS from Stanford University.

He was a founder and held the position of Vice President in Penware and atPos (now part of Symbol). He recruited the team and directed the design and development of the company's PDA, Point of Sale, enterprise, and e-commerce applications. He provided technical support in closing large deals and started several technology and business development initiatives in the company.

Earlier, he was a software scientist and an architect of heterogeneous object databases at Hewlett-Packard Laboratories. Prior to that, he was a system performance specialist at Hewlett-Packard's commercial and UNIX operating systems labs. He has published papers on computer performance evaluation and heterogeneous object databases and has also taught Computer Science at University of Oklahoma, U.C. Davis and Santa Clara University. He has authored and been granted several patents

#### **IEEE Professional Skills Courses**

#### new! Influential Communication

Date/Time: Tuesday, May 17, 8:30AM-4:30PM

Instructor: Barry Flicker

Location: at KLA-Tencor, San Jose -

Without a context of mutual value, trust and respect, techniques alone prove useless. This one-day course asks participants to evaluate their current communication environment according to these standards. We then begin to examine the three primary communication skills - clear goal setting, making our message audience-appropriate, and active/empathic listening - so that participants understand how to improve their working relationships in any situation. This is a highly experiential workshop applicable for people at every level of the organization.

#### **Session Objectives**

- Identify things that we may be doing or failing to do that contribute to difficult communication.

- Apply S.M.A.R.T. Criteria to set clear, mutually agreed upon objectives.

- Resolve questions of competence through effective application of the situational speaking model.

- Listen through difference to manage conflict and build influence.

Engineering Management & Components, Packaging and Manufacturing Technology Societies, SCV Chapters

#### **Key Topics**

- The Three Levels of Listening

- 8 Blocks to Effective Listening

- Clearing Listening Blocks

- How to Stop Defending

- Value Clarification: Out to Lunch Game

- Listening Through Differences

- How Values Filter What We Hear

- The Communication Triangle

- SMART criteria for Clear Communication

- Situational Speaking

## Improve your skills – register for a skills class. Bring a team!

For complete information and registration form, see our Chapter website, right-hand column:

www.cpmt.org/scv/

### SCV Lasers and ElectroOptics

## **TUESDAY APRIL 5**

### Semiconductor Ultraviolet Optical Sources: Status, Challenges, and Applications

Speaker: Dr. Noble Johnson, Palo Alto Research

Center

Time: Networking and Pizza Social at 7:00 PM;

Presentation at 8:00

Place: National Semiconductor Credit Union

Auditorium, 955 Kifer Road, Sunnyvale

RSVP: by email to rsvp-scv-leos@ieee.org

Web: ewh.ieee.org/r6/scv/leos/

Dr. Noble Johnson received his Ph.D. degree from Princeton University in 1974 under a National Defense Graduate Fellowship. From 1974 to 1976 he worked at SRI International (Menlo Park, CA) in the Radiation Physics Group of the Physical Sciences Division. In 1976 he joined the Xerox Palo Alto Research Center (now the Palo Alto Research Center) as a Member of the Research Staff in the Electronic Materials Laboratory. There he is a Principal Scientist and Manager of Optoelectronic Materials and Devices. He has conducted experimental research in the general areas of electronic materials and devices. Dr. Johnson has published over 330 research papers in technical journals and conference proceedings, has organized several topical and international conferences, has served as an editor of five books, and is an inventor on ten patents. In 1987 Dr. Johnson received a Distinguished Senior U.S. Scientist Award from the Alexander von Humboldt Foundation, Germany, and in 1988 he worked in residence at the Institute for Applied Physics, University of Erlangen-Nürnberg, Germany. He received awards for excellence in science and technology from Xerox PARC in 1987 and 1997 and from PARC in 2003. As Manager of the Optoelectronic Materials and Devices Program he has guided the activities of a world-class R&D team that has successfully developed violet and ultraviolet lasers and which has made major contributions to fundamental understanding of the material and devices. Dr. Johnson is a fellow of the American Physical Society and a fellow of the Institute of Electrical and Electronics Engineers.

Over the past 40 years semiconductor optical sources, light emitting diodes (LEDs) and laser diodes (LDs), have been displacing conventional light sources and gaseous lasers in commercial applications throughout the near infrared (IR) and visible regions of the spectrum. And in many cases, newer semiconductor sources with improved performance have displaced older semiconductor sources; an example currently in progress is the replacement of red LDs in DVDs by violet LDs for the next generation Blue-Ray or HD-DVD format.

The new frontier in the development of semiconductor sources is the ultraviolet (UV). This LDs already effort is well underway, with demonstrated in the AlGaInN materials system down to 340 nm and LEDs operating below 280 nm. Such UV sources will enable miniaturization and/or cost/performance improvements for existing UVbased systems, with proliferation of existing functionality and realization of new applications. In comparison with existing UV gas sources (lasers and lamps) and other more complex and costly solid-state lasers (e.g., photo-pumped lasers and frequencytripled /quadrupled lasers), semiconductor UV advantages offer several compactness, low power consumption, low cost, and long lifetimes. These features will drive a host of commercial applications in areas that include biotechnology, water purification, and UV curing. The first area of commercialization will likely be replacement of Hg lamps for germicidal and (lowpower) UV curing applications. In addition, as with any truly destabilizing technology, there will likely be completely new applications that have yet to be conceived.

### SCV Electromagnetic Compatibility

## **TUESDAY APRIL 12**

# EMI Analysis of Complex Systems; and Electrostatic Discharge - It Failed! How to Find the Root Cause!

Speaker: Dr. David Pommerenke, UMR

Time: Social 5:30 PM, Presentation 7:00 PM

Place: Applied Materials Bowers Cafeteria, 3090

Bowers Ave., Santa Clara

RSVP: not required Info: www.scvemc.org/

**David Pommerenke** is associated professor at the EMC laboratory at UMR. Dr. Pommerenke's speciality is the combination of electronics and electromagnetics. Such problems can be found in intentional or unintentional disturbances of circuits, Signal Integrity of fast networks and other situations in which the circuit behavior is dominated by "everything that is not on the circuit diagram". His interests are: EMC, ESD, Electronics, Signal Integrity, measurement instrumentations and testing. Before joining UMR he worked as an EMC Engineer at HP for five years. He is member of the ESD standard setting group within IEC TC77b.

#### Part I: EMI Analysis of complex systems

Many methods and tools exist for the analysis of EMI of complex systems. Examples are different probing methods, time domain data analysis, frequency domain data analysis at different bandwidths and the methods that fall between time and frequency domain, such as zero span spectrum analysis and Joint-Time-Frequency Analysis techniques such as Short Term FFT and wavelet analysis.

This talk will show the application of different data analysis techniques for complex systems. Special emphasis is given on explaining the methods and on showing when which method provides the better insight, not on promoting one or the other method.

## Part II: Electrostatic Discharge - It failed! How to find the root cause!

Assume a system has failed an ESD test. Of course, one could improve shielding, but isn't it better to exactly understand which electrical net or IC had been affected and, consequently, just apply a small change to the board or software?

The talk explains methods on how to find the root cause of ESD failures by systematic local injection and how to probe signals with GHz bandwidth, while applying ESD to the system. It will show examples of systems that experienced ESD failures that have been located using this technique. Further, it will discuss how IC-level EMC will influence ESD design.

TEA

Device Thermal Characterization Package Thermal Characterization Thermal Test Boards Thermal Test Equipment & Fixtures

#### **Bernie Siegal**

Thermal Engineering Associates. Inc. 650-961-5900

info@thermengr.com www.thermengr.com

## **TUESDAY APRIL 12**

## VLSI Devices for Analog and Mixed-Signal Applications

Speaker: Dr. Jason Woo, UCLA

Time: Pizza social (free) at 6:00pm;

Presentation at 6:15pm

Place: National Semiconductor Corp. Building 31

Large Auditorium, 955 Kifer Road,

Sunnyvale

RSVP: not required

Info: Philippe Jansen, philippe.jansen@nsc.com

**Dr. Jason C.S. Woo** received the B. A. Sc. (Hons) degree in engineering science from the University of Toronto, Canada, in 1981, and the M. S. and Ph. D. degrees in electrical engineering from Stanford University in 1982 and 1987, respectively. He joined the department of electrical engineering of UCLA in 1987, where he is currently a professor. He has done work on low-temperature devices for VLSI applications, SOI BiCMOS, SiGe BiCMOS and other novel devices. He has authored and co-authored over 160 papers in technical journals and refereed conference proceedings in these areas.

As scaling of CMOS approaches sub-100nm, many difficulties are encountered such as short-channel effects, device performance improvement limits, severe reliability issues and gate leakage issues. In terms of analog behavior, these problems translate into lower intrinsic gain and higher non-linearity. This talk will discuss the scaling behavior of scaled CMOS for analog/RF applications. A novel device architecture which has superior analog behavior will also be discussed.

SCV Microwave Theory & Techniques Chapter

### Designs for the High-Speed, Broadband Information Age

SiGe, RF-CMOS, SiC, GaN technologies

• Wednesday, April 13, 2005

Seminar: 8:30 AM – Noon

Registration/Breakfast: 8 AM – 8:30 AM

Santa Clara Convention Center

- In conjunction with IEEE WESCON'05

- Includes free admission to WESCON exhibits

More information on Page 12

### SCV Antennas and Propagation

### **WEDNESDAY APRIL 13**

## A Spatial Channel Model for Multiple-Antenna Systems

Speaker: Dr. Ada Poon, SiBeam Inc. Time: 6:00 p.m. (pizza & soda),

6:30 p.m. presentation

Cost: none

Place: Cogswell College (Boardroom), 1175

Bordeaux Dr, Sunnyvale

RSVP: d by email to Greg Manassero at

greg.manassero@ieee.org

Web: www.ewh.ieee.org/r6/scv/scv\_aps.html

Dr. Ada S. Y. Poon received the B.Eng and M.Phil. degrees in Electrical and Electronic Engineering from the University of Hong Kong in 1996 and 1997 respectively, and received the M.S. and Ph.D. degrees in Electrical Engineering and Computer Sciences from the University of California at Berkeley in 1999 and 2004 respectively. From Oct. 2003 to Jan. 2005, she was a senior researcher at Intel Corporation, Santa Clara, where she researched feedback schemes for multiple-antenna systems and implementation of baseband processors for future flexible radios. Currently, she is with SiBeam, Inc., Fremont, a startup company designing Gigabit wireless transceivers leveraging 60 GHz CMOS technology and multiple-antenna systems. research interests are wireless communications and information theory, VLSI signal processing, and reconfigurable architecture for wireless systems.

Conventional multi-input multi-output (MIMO) models are not efficient for assessing the benefits of multiple-antenna systems with an area limitation on antenna arrays in realistic propagation environments. Physical models, though capturing these factors, are too complex for tractable analysis. This talk presents a spatial channel model that takes into account these factors without sacrificing analytical tractability. In the model, the Green function for radiation is adapted to account for the array area limitation, and the clustering of physical paths observed in recent spatial channel measurements is exploited to obtain a concise description of channel scattering. Based on these modeling strategies, for a spherical array of effective aperture A in a physical environment of total angular spread Omega in solid angle, the number of independent channels (spatial degrees of freedom) is 2AOmega. The result helps assess the optimal number of antennas that should be put on the given transmit and receive areas in both single-user and multi-user environments. The analysis also sheds light on transceiver architectures that would utilize channel scattering more efficiently.

Professional Consulting Services to assist clients in developing and executing any elements of Reliability throughout the Organization and Product Life Cycle.

•Goal Setting • MTBF Predictions • HALT • HASS/ESS •Assessments • FMECA • DVT/V&V • EOL Assessment •Program Plans • DoE • Rel Demos • Training/teaching •Gap Analysis • CAPA/CLCA • Life Tests ...and more

OPS ALACARTE PIONEERED Reliability Integration<sup>SM</sup>

– Using multiple tools together to increase the power and value of any Reliability Program.

## **WEDNESDAY APRIL 13**

## Where is the RFID Puck Going Next?

Speaker: Sam Patadia, VP of Engineering, eSmart

Source, Inc.

Time: 6:00 p.m. (pizza & soda, \$1),

6:30 p.m. presentation

Place: National Semiconductor Credit Union,

Bldg. 31, 955 Kifer Rd., Sunnyvale

RSVP: by email to rsvp@comsocscv.org

Web: www.comsocscv.org

See also: "Packaging Technology for RF RFID" on

page 10

Sam Patadia is a senior information technology professional with over 25 years experience as project manager, software architect, systems engineer, instructor, and trainer in RFID application integration, software design and development, middleware, and data acquisition and control systems. Sam has taught several short courses in RFID technology at places like the Mitre Institute, National Institute of Standards and Technology, Software Development Forum, San Jose State University, and the Singapore Manufacturer's Federation.

He holds a bachelor's degree in Mechanical Engineering from the University of North Carolina and a Master's degree in Computer Aided Engineering from the same institution. He lives with his family in San Jose and enjoys visiting and photographing places with rocks, water, and trees.

Ever since the announcement of mandates to suppliers of Wal-Mart, Target, Albertsons, Best Buy and the U.S. Department of Defense to use radio frequency identification (RFID) to track pallets and cartons in the supply chain, RFID has garnered major interest in all corners of the high-tech industry. The casino industry is just the latest to find new uses for RFID technology. The United States and other nations are incorporating it into passports to catch counterfeits. Other people are planning to use RFID in mobile resource management. That means using both passive and active RFID technologies to track assets, work-in-process, returnable containers and vehicles in a close-loop supply chain. ABI Research estimates the RFID hardware and software market will surpass \$4.6 billion by 2008 due to increased market activity, shipments, and mandates. Activities like supply chain, retail, consumer goods, and defense activity will continue to fuel growth, along with increased innovation in homeland security and smart payment markets.

The talk will briefly discuss various components of RFID eco system, role of EPCglobal and various factors which is fueling this growth in the market.

SCV Components, Packaging & Mfg Technology Chapter

## Packaging Technology for RF & RFID

- Wednesday, April 13, 2005

- Seminar: 1:00 5:30 PM

- Registration: begins at Noon

- Santa Clara Convention Center

- In conjunction with IEEE WESCON'05

- Includes free admission to WESCON exhibits

- Plenty of free parking

For further information, see:

www.cpmt.org/scv/

### SCV Engineering in Medicine and Biology

## **WEDNESDAY APRIL 20**

# Tactile Pressure Imaging: A New Tool For In Vivo Physiological Assessment for Gastroenterology

Speaker: Tom Parks, Ph.D., Sierra Scientific

Instruments, Inc.

Time: Dinner with the speaker in the Stanford

Hospital cafeteria at 6:15 PM (No

reservation needed); Presentation at 7:30 PM

Place: Clark Center Auditorium (see website for

map)

RSVP: not required

Web: www.ewh.ieee.org/r6/scv/embs/pages/

upcoming.html