1st Printing, June 1976 2nd Printing (Rev), October 1977 3rd Printing, August 1979

Copyright <sup>®</sup> 1976, 1977, 1979 by Digital Equipment Corporation

The reproduction of this workbook, in part or whole, is strictly prohibited. For copy information contact the Educational Services Department, Digital Equipment Corporation, Bedford, Massachusetts 01730.

Printed in U.S.A.

## INTRODUCTION TO MINICOMPUTERS

# Logic and Hardware Basics

Student Workbook

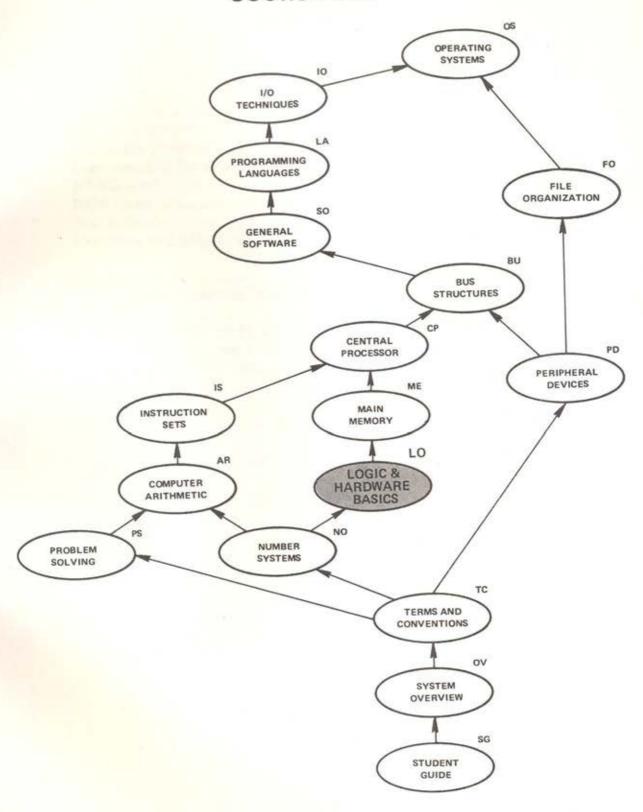

# **COURSE MAP**

# CONTENTS

| Introduction                     | 1  |

|----------------------------------|----|

| Logic Gates                      | 3  |

| Objectives and Sample Test Items | 3  |

| AND Gate                         |    |

| Inclusive OR Gate                | 10 |

| Exclusive OR Gate                | 12 |

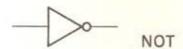

| NOT Gate (Inverter)              | 14 |

| Exercises and Solutions          | 17 |

| NAND Gate                        | 21 |

| NOR Gate                         | 24 |

| Summary                          |    |

| Exercises and Solutions          | 29 |

| Basic Circuits                   | 37 |

| Objectives and Sample Test Items | 37 |

| Flip-Flops                       |    |

| Set-Reset (RS) Flip-Flops        | 42 |

| Clock-Data (D-Type) Flip-Flops   | 43 |

| Exercises and Solutions          | 45 |

| Registers                        | 49 |

| Buffer Registers                 | 49 |

| Shift Registers                  | 49 |

| Counters                         | 51 |

| Exercises and Solutions          | 53 |

| Appendix A More Complex Circuits | 59 |

# Logic and Hardware Basics

#### Introduction

Many people are awed by the apparent complexities of digital computer electronic circuits or "hardware." However, no matter how complex computer hardware may seem to be, it can be reduced to a small number of elemental components called "logic gates." These logic gates are the basic building blocks of any digital computer system – from the simplest to the most sophisticated computer in existence.

These basic logic gates, in themselves, perform extremely simple functions. However, by wiring them together in various combinations, they can be used to form more complex components such as adders and counters. These latter circuits can then be further combined to form extremely sophisticated logic elements.

It must be stressed that no matter how complex computer logic may appear at first glance, it can always be reduced to a combination of the basic logic gates that will be covered in this lesson. Therefore, it is quite important to obtain a thorough understanding of these basic gates.

This module contains two lessons. The first lesson describes the six basic *logic gates* used by computers. The second lesson describes how certain basic gates are used together to form such components as *flip-flops*, registers, and counters.

It should be noted that there are two basic approaches to describing logic gates. One is the conventional, theoretical approach – using 1 and 0 (true and false) to represent the two digital voltage levels in the hardware. The other approach, called Functional Boolean, does not uniquely assign true and false to digital voltage levels. Consequently, the Functional Boolean approach has many variations.

This module covers the conventional, theoretical approach. This approach provides the foundation for more advanced study.

# **Logic Gates**

## OBJECTIVES -

- Given six logic symbols and six functions, be able to match each symbol with its function.

- Given six truth tables and six logic functions, be able to match each truth table with its corresponding logic function.

- Given a table of six logic gates and their inputs and outputs and a list of six mathematical expressions, be able to match each logic function with its mathematical expression.

## -SAMPLE TEST ITEMS -

Match each of these logic symbols with the function it represents by writing the correct letter in the space provided.

| Logic Symbol | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | and the same of th |

|              | HI HI WAS THE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ->           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## **Functions**

- a. XOR

- d. OR

- b. NOR

- e. NAND

- c. AND

- f. NOT

## SAMPLE TEST ITEMS -

Six truth tables and six logic functions are given below. Match each truth table with the logic function it represents.

| a. | Inpu | ts | Output |

|----|------|----|--------|

|    | Α    | В  | С      |

|    | 0    | 0  | 0      |

|    | 0    | 1  | 1      |

|    | 1    | 0  | 1      |

|    | 1    | 1  | 0      |

| ο. | Inpu | ts | Output |

|----|------|----|--------|

|    | Α    | В  | С      |

|    | 0    | 0  | 1      |

|    | 0    | 1  | 1      |

|    | 1    | 0  | 1      |

|    | 1    | 1  | 0      |

| C. | Inpu | ts | Output |

|----|------|----|--------|

|    | Α    | В  | С      |

|    | 0    | 0  | 0      |

|    | 0    | 1  | 1      |

|    | 1    | 0  | 1      |

|    | 1    | 1  | 1      |

| d. | Inpu | ts | Output |

|----|------|----|--------|

|    | Α    | В  | С      |

|    | 0    | 0  | 1      |

|    | 0    | 1  | 0      |

|    | 1    | 0  | 0      |

|    | 1    | 1  | 0      |

| e. | Inpu | ts | Output |

|----|------|----|--------|

|    | Α    | В  | С      |

|    | 0    | 0  | 0      |

|    | 0    | 1  | 0      |

|    | 1    | 0  | 0      |

|    | 1    | 1  | 1      |

| f. [ | Input | Output |

|------|-------|--------|

|      | 0     | 1      |

|      | 1     | 0      |

| Logic Function | Truth Table |

|----------------|-------------|

| AND            | ·           |

| OR             | 8           |

| NOR            | 2           |

| NOT            |             |

| NAND           |             |

| YOR            |             |

### SAMPLE TEST ITEMS -

3. Determine the mathematical expression that illustrates the logical relationships between the inputs and output of the six logic gates listed below. Write the number of the correct mathematical expression in the space provided.

| Gate | Inputs | Output | Mathematical<br>Expression |

|------|--------|--------|----------------------------|

| AND  | A,B    | С      |                            |

| OR   | A,B    | С      | <del></del>                |

| NOR  | A,B    | С      |                            |

| NOT  | Α      | С      |                            |

| NAND | A,B    | С      |                            |

| XOR  | A,B    | С      |                            |

# **Mathematical Expressions**

1.

$$C = \overline{A} \cdot \overline{B}$$

4.  $C = A + B$

2.

$$C = A \cdot B$$

5.  $C = \overline{C}$

3.

$$C = \overline{A} + \overline{B}$$

3.

$$C = \overline{A} + \overline{B}$$

6.  $C = A + B$

Mark your place in this workbook and view Lesson 1 in the A/V program, "Logic Gates."

Logic gates are simple electronic circuits that implement elementary logical functions. Logic gates serve as the basic building blocks for all digital computers. Computer operations, no matter how complex, are performed by using various combinations of these basic logic gates. The six most common types of logic gates are covered in this lesson. Each gate is named after the logical function that it performs. These gates are:

- 1. AND

- 2. OR

- 3. XOR (exclusive OR)

- 4. NOT (inverter)

- 5. NAND (not and)

- 6. NOR (not or)

Each of these gates, except the NOT gate (inverter), has two or more input lines but only one output line. The NOT gate has one input line and one output line.

When discussing logic gates, it is quite common to use the terms "true" and "false" when referring to the input and output states of the gate. In this workbook "true" is the equivalent of binary 1 and "false" is the equivalent of binary 0.

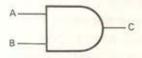

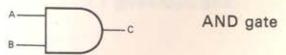

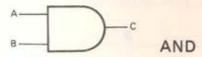

#### AND Gate

The AND gate provides a true output only when all of the inputs are true. In other words, the gate generates a binary 1 output when certain logic conditions are satisfied as indicated by a binary 1 on every input line. Thus, if the AND has two input lines, it can be stated that: 1 AND 1 = 1.

As an example, the output of an AND gate might be used to trigger some other logic element. The element is to be triggered only if certain conditions exist. If these conditions are set up as inputs to the AND gate, the element will be triggered only when the pre-defined conditions exist.

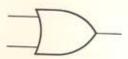

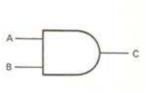

The standard logic symbol for an AND gate is shown in Figure 1. Notice that only two inputs are shown; however, an AND gate can have more than two inputs but never more than one output. The two input lines are labeled "A" and "B" while the output line is labeled "C."

Figure 1 The AND Gate

A chart can be constructed to describe the operation of any logic circuit. This chart lists every possible combination of input values (binary 1s and 0s) and the output resulting from each combination of inputs. Some people substitute the words "true" and "false" for the values "1" and "0" when using a chart of this type. That's why this chart, or table, is commonly referred to as a "truth table" even though 1s and 0s are used.

Table 1 is a truth table for a 2-input AND gate. It lists every possible combination of input values and shows the appropriate output for each combination of inputs. Notice that there is an output only when both inputs are true (or 1s). Thus, we can say that "C" (the output) is true when inputs "A" AND "B" are true.

Table 1 2-Input AND Gate - Truth Table

| Inp | uts | Output |

|-----|-----|--------|

| Α   | В   | С      |

| 0   | 0   | 0      |

| 0   | 1   | 0      |

| 1   | 0   | 0      |

| 1   | 1   | 1      |

When constructing truth tables for logic gates that have many inputs, it is useful to know how many input combinations are possible. This can be calculated by  $2^n$  where "n" equals the number of input lines. For example, you have just seen a table for a 2-input AND gate. Using the formula  $2^n$ , we substitute the number of inputs (2) for the "n" and come up with  $2^2$ . We know that  $2^2 = 4$ . Therefore, there are four possible input combinations in the truth table.

Table 2 below is a truth table for a 3-input AND gate. By using the formula 2<sup>n</sup>, we know that the input combinations will be 2<sup>3</sup> (or 8). If you look at the table, you will see that there are 8 input combinations. Notice also that the output is true *only* when *all three inputs are true* . . . or 1s. We can say that "D" (the output) is true only when inputs "A" AND "B" AND "C" are true.

Table 2 3-Input AND Gate - Truth Table

| In | Inputs |   | Output |

|----|--------|---|--------|

| А  | В      | С | D      |

| 0  | 0      | 0 | 0      |

| 0  | 0      | 1 | 0      |

| 0  | 1      | 0 | 0      |

| 0  | 1      | 1 | 0      |

| 1  | 0      | 0 | 0      |

| 1  | 0      | 1 | 0      |

| 1  | 1      | 0 | 0      |

| 1  | 1      | 1 | 1      |

Another method of describing the AND function is to use a mathematical formula. Using a formula provides a precise shorthand notation for easy representation of digital logic. Let's go back to the 2-input AND gate. We know that the output ("C") is true only when both inputs ("A" and "B") are true. Therefore, we can express this relationship by using the formula:

C = A AND B

However, the relationship is normally expressed by using special logic notation. The AND function, for example, uses a large dot as the standard symbol. Thus, the AND function is normally expressed as:

$C = A \cdot B$

As another example, a 3-input AND gate is expressed by the formula:

$D = A \cdot B \cdot C$

where "D" represents the output of the gate, and "A," "B," and "C" represent the three inputs.

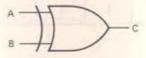

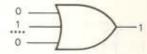

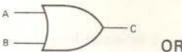

## Inclusive OR Gate

The inclusive OR gate provides a true output if either one input or the other input or both inputs are true. This gate produces a true output (binary 1) when at least one input logic condition is satisfied as indicated by a binary 1 on one of the input lines. Thus, we can say that: 1 OR 1 = 1.

As an example, assume that a certain logic element is to be turned on when any one of a number of conditions exist. These conditions can be set up as OR gate inputs. The output of the gate is connected to the logic element. Therefore, whenever one or more of the conditions exist, the OR gate will provide an output that will turn on the desired logic element.

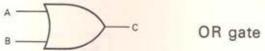

The standard logic symbol for an inclusive OR gate is shown in Figure 2. Notice that only two inputs are shown; however, an inclusive OR gate can have more than two inputs but never more than one output. The two input lines are labeled "A" and "B" while the output line is labeled "C."

Figure 2 The Inclusive OR Gate

This gate is called an *inclusive* OR because any *one or more* true inputs will provide a true output. In other words, if there were four input lines, a true input on lines 1 through 4, inclusive, would provide a true output. Whenever the term "OR" gate is used by itself, it refers to the "inclusive OR" gate.

Table 3 is a truth table for a 2-input inclusive OR gate. It lists all possible combinations of input values and shows the output for each combination of inputs.

Table 3 2-Input OR Gate - Truth Table

| Inputs |   | Output |

|--------|---|--------|

| Α      | В | С      |

| 0      | 0 | 0      |

| 0      | 1 | 1      |

| 1      | 0 | 1      |

| 1      | 1 | 1      |

Notice in Table 3 that the *output* of an inclusive OR gate is zero only when *all* inputs are zero. On the other hand, the output is one if *either* or *both* inputs are one.

Table 4 is a truth table for a 3-input inclusive OR gate. Again, notice that the output is zero only when all inputs are zero.

Table 4 3-Input OR Gate - Truth Table

|   | Inputs | Output |   |

|---|--------|--------|---|

| Α | В      | С      | D |

| 0 | 0      | 0      | 0 |

| 0 | 0      | 1      | 1 |

| 0 | 1      | 0      | 1 |

| 0 | 1      | 1      | 1 |

| 1 | 0      | 0      | 1 |

| 1 | 0      | 1      | 1 |

| 1 | 1      | 0      | 1 |

| 1 | 1      | 1      | 1 |

A mathematical formula can also be used to represent the inclusive OR function. For example, operation of a 2-input inclusive OR gate can be expressed by the formula:

$$C = A OR B$$

However, the inclusive OR function is usually represented by a special symbol (+). The inclusive OR function is normally expressed as:

$$C = A + B$$

In the case of a 3-input OR gate, the mathematical formula would be:

$$D = A + B + C$$

The formula could be stated: "D" is true if "A" OR "B" OR "C" is true.

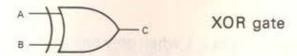

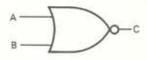

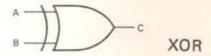

### **Exclusive OR Gate**

The purpose of the exclusive OR gate is to provide a true output if either one input or the other input, but not both, is true. In other words, the gate generates a true output (binary 1) when any one, but not more than one, logic condition is satisfied.

As an example, assume that a certain logic element is to be turned on only if one of a number of conditions exist. The element is to remain off if none of the conditions exist, or if more than one condition exists. This problem could be satisfied by using an exclusive OR gate output as the input to the logic element.

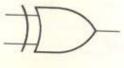

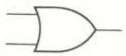

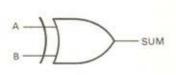

The standard logic symbol for an exclusive OR gate is shown in Figure 3. Note that the exclusive OR gate is usually referred to as an XOR gate to differentiate it from an inclusive OR gate. Notice that only two inputs are shown in the figure; however, an exclusive OR gate can have more than two inputs but never more than one output. The input lines are labeled "A" and "B" while the output line is labeled "C."

Figure 3 The Exclusive OR (XOR) Gate

This gate is called an exclusive OR because any one true input, exclusively, will provide a true output. In other words, if there is more than one true input, the output will be false.

Truth tables for the exclusive OR (XOR) and inclusive OR functions are compared in Table 5.

Table 5 XOR Versus Inclusive OR - Truth Tables

| -   | -   | - |   | - | _ |  |

|-----|-----|---|---|---|---|--|

| . ٦ | ur. | _ | v | × | _ |  |

| - 1 |     |   |   |   |   |  |

| Inputs |   | Output |

|--------|---|--------|

| Α      | В | С      |

| 0      | 0 | 0      |

| 0      | 1 | 1      |

| 1      | 0 | 1      |

| 1      | 1 | 0      |

Inclusive OR

| Inp | uts | Output |

|-----|-----|--------|

| A   | В   | С      |

| 0   | 0   | 0      |

| 0   | 1   | 1      |

| 1   | 0   | 1      |

| 1   | 1   | 1      |

As you can see in Table 5, the XOR and inclusive OR gates are identical except for the *last* condition. With *inclusive* OR, the output is 1 when both inputs are 1s. However, with XOR, the output is 0 when both inputs are 1s.

In summary, the output of an XOR gate is 1 if either input, but not both, is 1. If both inputs are 0, or if both inputs are 1, the output is 0.

The XOR rules are true even when dealing with gates having more than two inputs as shown in Table 6. Notice that the output is 1 only when a single input is 1.

Table 6 3-Input XOR Gate

| T.A. Ti | Inputs | Output |   |

|---------|--------|--------|---|

| Α       | В      | С      | D |

| 0       | 0      | 0      | 0 |

| 0       | 0      | 1      | 1 |

| 0       | 1      | 0      | 1 |

| 0       | 1      | 1      | 0 |

| 1       | 0      | 0      | 1 |

| 1       | 0      | 1      | 0 |

| 1       | 1      | 0      | 0 |

| 1       | 1      | 1      | 0 |

A mathematical formula can also be used to represent the XOR function. For example, operation of a 2-input exclusive OR (XOR) gate can be expressed by the formula:

However, the XOR function is usually represented by a special symbol which is a plus sign with a circle ( ). Thus, the XOR function is normally expressed as:

$$C = A \oplus B$$

In the case of a 3-input XOR gate, the formula would be:

$$D = A \oplus B \oplus C$$

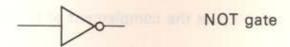

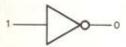

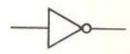

# NOT Gate (Inverter)

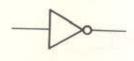

The purpose of the NOT gate is to convert an input signal to its opposite (complementary) state. The NOT gate is often called an inverter because it inverts the input signal. For example, if the input signal is high, the NOT gate inverts it to a low signal.

The standard symbol for a NOT gate is shown in Figure 4. There are three important items to notice in the figure:

- The NOT gate is the only gate with a single input and a single output line.

- A bar drawn over the input or the output indicates the false state.

If the input is "A," the output is "NOT A."

- 3. A small circle drawn on either the input or output line indicates the false or "not" state.

Figure 4 The NOT Gate

Table 7 is a truth table for the NOT gate. Notice that there are only two possible inputs to the gate.

Table 7 NOT Gate - Truth Table

| Input | Output |

|-------|--------|

| 0     | 1      |

| 1     | 0      |

We can also use a mathematical formula to represent the NOT function. We express the NOT function as:

$$A = NOT A$$

or

$$NOTA = A$$

The NOT function is usually represented by a standard symbol – a bar drawn over the false state. Thus, the NOT function is normally expressed as:

$A = \overline{A}$

ОГ

$\overline{A} = A$

The following formula is used to indicate how many input combinations are possible for a given logic gate:

Possible Inputs = 2<sup>n</sup>

If the logic gate has five input lines, how many input combinations are possible? (Circle the correct answer.)

- a. 16

- b. 8

- c. 32

- d. 12

- Using binary 1s and 0s, complete the truth table for each of the following logic gates:

AND

| uts | Output   |

|-----|----------|

| В   | С        |

|     |          |

|     |          |

|     |          |

| ֡   | uts<br>B |

OR

| Inp | uts | Output |

|-----|-----|--------|

| Α   | В   | С      |

|     |     |        |

|     |     |        |

|     |     |        |

XOR

| uts | Output |

|-----|--------|

| В   | С      |

|     |        |

|     |        |

|     |        |

|     | B B    |

NOT

The following formula is used to indicate how many input combinations are possible for a given logic gate:

Possible Inputs = 2<sup>n</sup>

If the logic gate has five input lines, how many input combinations are possible? (Circle the correct answer.)

- a. 16

- b. 8

- (c) 32

- d. 12

- Using binary 1s and 0s, complete the truth table for each of the following logic gates:

AND

| Inp | uts | Output |

|-----|-----|--------|

| Α   | В   | С      |

| 0   | 0   | 0      |

| 0   | 1   | 0      |

| 1   | 0   | 0      |

| 1   | 1   | 1      |

OR

| Inp | Inputs |        |  |

|-----|--------|--------|--|

| Α   | В      | Output |  |

| 0   | 0      | 0      |  |

| 0   | 1      | 1      |  |

| 1   | 0      | 1      |  |

| 1   | 1      | 1      |  |

XOR

| Inp | Inputs |        |  |

|-----|--------|--------|--|

| Α   | В      | Output |  |

| 0   | 0      | 0      |  |

| 0   | 1      | 1      |  |

| 1   | 0      | 1      |  |

| 1   | 1      | 0      |  |

NOT

| Input | Output |

|-------|--------|

| 0     | 1      |

| 1     | 0      |

| EXERCISES |  | E | X | E | R | CI | S | ES |

|-----------|--|---|---|---|---|----|---|----|

|-----------|--|---|---|---|---|----|---|----|

3. Draw the gate that outputs a 1 only when both inputs are a 1.

4. Draw the gate that outputs the complement of the input.

5. Draw the gate that outputs a 1 when only one of its inputs is a 1.

6. Draw the gate that outputs a 1 when at least one of its inputs is a 1.

3. Draw the gate that outputs a 1 only when both inputs are a 1.

4. Draw the gate that outputs the complement of the input.

Draw the gate that outputs a one when any one of the inputs is a one.

Draw the gate that outputs a one when at least one of its inputs is a one.

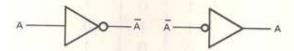

There are two additional gates to be covered in this module: the NAND gate and the NOR gate.

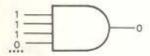

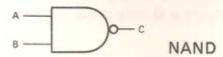

#### NAND Gate

The word "NAND" is a contraction for the words "not and." In order to understand the function of a NAND gate, it is necessary to review the AND and the NOT gates.

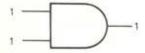

Figure 5 illustrates a standard AND gate. When both inputs are true (binary 1s), the output is also true (binary 1).

Figure 5 A Standard AND Gate

Figure 6 illustrates a standard NOT gate. Notice here that a true input (binary 1) results in a false output (binary 0).

Figure 6 A Standard NOT Gate

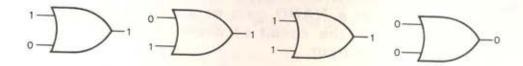

Figure 7 illustrates what happens if the output of the AND gate is connected to the input of the NOT gate. Notice that the input to this circuit consists of true inputs (binary 1s) but the output is false (binary 0). This is the basic function that is performed by a NAND gate.

Figure 7 Connecting an AND and NOT Gate

The function of a NAND gate, therefore, is to provide a false output when all of the inputs are true. In other words, the gate generates a binary 0 output when all inputs are binary 1s. The NAND gate will produce a binary 1 output if any input line contains a binary 0.

As an example of NAND gate use, assume that some logic circuit is to be turned off whenever certain conditions exist simultaneously. Each of these conditions can be represented by one input line to the NAND gate. The output of the gate is then connected to the logic circuit. Thus, when all conditions are true (a 1 on each NAND gate input line), the NAND gate will produce a false (or binary 0) output which will turn off the logic circuit.

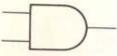

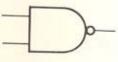

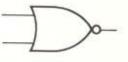

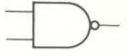

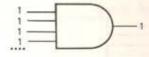

The standard logic symbol for a NAND gate is shown in Figure 8. Notice that only two inputs are shown. However, a NAND gate can have more than two inputs but never more than one output. The two input lines are labeled "A" and "B" while the output line is labeled "C."

Figure 8 The NAND Gate

Truth tables for the NAND and AND functions are compared in Table 8. As shown in the table, the outputs of the NAND gate and AND gate are exactly *opposite*. With a NAND gate, the output is a 1 whenever there is a 0 on either or both input lines. The output is 0 only when there are 1s present on all input lines.

Table 8 NAND Versus AND - Truth Tables

| Inp | uts | Output | Inp | uts | Output |

|-----|-----|--------|-----|-----|--------|

| A   | В   | С      | A   | В   | c      |

| )   | 0   | 1      | 0   | 0   | 0      |

| )   | 1   | 1      | 0   | 1   | 0      |

|     | 0   | 1      | 1   | 0   | 0      |

|     | 1   | 0      | 1   | 1   | 1      |

|     |     | R      |     |     | -      |

#### NOTE

When logic circuits are designed, AND and NAND gates are used to identify a specific set of input conditions. These gates output a unique value only when the specific inputs occur. In this respect, the AND gate and the NAND gate are alike – they both respond to the input condition of all 1s with a unique output. The difference is that the AND gate outputs the unique output value of one, and the NAND outputs the unique value of zero. The selection of a NAND gate or an AND gate depends on the circuit or device that is to receive its output.

A mathematical formula can be used to represent the NAND function. Although NAND is a contraction for NOT AND, it is interesting to note that the formula can be expressed in terms of inclusive OR. A 2input NAND gate, for instance, is expressed by the formula:

$$C = \overline{A} + \overline{B}$$

(C equals Not A or Not B)

Thus, when both inputs are binary 0 ( $\overline{A}$  and  $\overline{B}$ ), the output is binary 1. If either input is a binary 0 ( $\overline{A}$  or  $\overline{B}$ ), the output is binary 1. However, when both inputs are binary 1 (A and B), the output (C) is binary 0. Therefore, if either one or both inputs are false, the output is true. Notice the similarities between the two formulas:

OR

$$C = A + B$$

(C equals A or B)

NAND  $C = \overline{A} + \overline{B}$  (C equals Not A or Not B)

The NAND gate can also be expressed in terms of the AND function by using the formula:

$$\overline{C} = A \cdot B$$

This formula states that C is false when A and B are true.

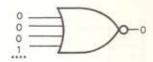

## NOR gate

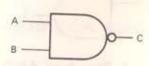

The word "NOR" is a contraction for the words "not or." In order to understand the function of a NOR gate, it is necessary to review the inclusive OR gate and the NOT gate.

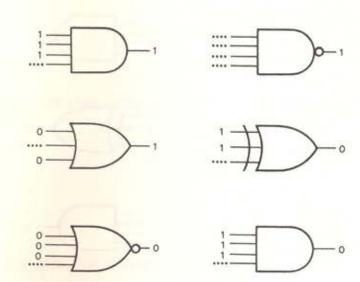

Figure 9 illustrates the possible conditions of an inclusive OR gate. Notice that when either or both inputs are true (binary 1), the output is also true (binary 1).

Figure 9 Inclusive OR gate - Possible Conditions

Figure 10 illustrates a standard NOT gate. Notice here that a true input (binary 1) results in a false output (binary 0).

Figure 10 A Standard NOT Gate

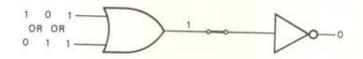

Figure 11 shows what happens if the output of the above OR gate is connected to the input of the above NOT gate. Notice that whenever either one or both inputs to the *circuit* are true (binary 1), the output of the *circuit* will be *false* (binary 0). This is the same basic function that is performed by the NOR gate.

Figure 11 Connecting an OR and NOT Gate

The function of a NOR gate is to provide a false output when either one or both inputs are true. The opposite is also true. If no input line is true (both inputs false), then the NOR gate will generate a true output.

A NOR gate might be used to turn on some logic circuit only if certain conditions do not exist. If any one of these conditions do exist, the NOR gate produces a false output, preventing the logic circuit from being turned on.

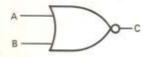

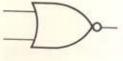

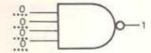

The standard logic symbol for a NOR gate is shown in Figure 12. Although only two inputs are shown, a NOR gate can have more than two inputs but never more than one output. Notice also that the NOR gate is an inclusive OR symbol with a small circle on the output line to indicate that the output is false when the inputs are true (i.e., the circle represents the NOT function).

Figure 12 The NOR Gate

### NOTE

As with AND and NAND, OR and NOR are also functionally the same – OR and NOR both have their desired output when at least one input is a one. The difference is that the desired output of an OR gate is one, while the desired output for a NOR gate is zero. The selection of an OR gate or a NOR gate depends on the circuit or device that is to receive the output.

Truth tables for the NOR and OR functions are compared in Table 9. As shown in the table, the NOR gate and OR gate outputs are exactly the *opposite*. With a NOR gate, the output is 0 whenever there is a 1 on either or both input lines. The output is 1 only when there are 0s present on all input lines.

Table 9 NOR vs OR - Truth Tables

| Inp | uts | Output | Inp | uts | Output |

|-----|-----|--------|-----|-----|--------|

| A   | В   | С      | A   | В   | C      |

| 0   | 0   | 1      | 0   | 0   | 0      |

| 0   | 1   | 0      | 0   | 1   | 1      |

| 1   | 0   | 0      | 1   | 0   | 1      |

| 1   | 1   | 0      | 1   | 1   | 1      |

A mathematical formula can be used to represent the NOR function. Although NOR is a contraction for NOT OR, it is interesting to note that the formula is expressed in terms of AND. A 2-input NOR gate, for instance, can be expressed by the formula:

$$C = \overline{A} \cdot \overline{B}$$

(C equals Not A and Not B)

Thus, the only time the NOR gate produces a true (binary 1) output is when both inputs are binary 0 (A AND B).

The NOR gate can also be expressed in terms of the OR function by using this formula:

$$C = \overline{A + B}$$

This formula states that C is true whenever the expression A or B is false. In other words, when both A and B are false, then C is true. However, if either A or B is true, then C will be false.

# Summary

Table 10 is a composite truth table for five of the logic gates that have been covered in this lesson. Only the inverter (NOT gate) has been left out because it is a single input device. Notice that the table also includes the standard logic symbol for each gate as well as the appropriate mathematical formula.

Table 10 Basic Logic Gates - Truth Table

| Inp     | uts          | Output (C) |           |         |                                                              |                                                   |  |  |

|---------|--------------|------------|-----------|---------|--------------------------------------------------------------|---------------------------------------------------|--|--|

| A       | В            | AND        | OR        | XOR     | NAND                                                         | NOR                                               |  |  |

| 0       | 0            | 0          | 0         | 0       | 1                                                            | 1                                                 |  |  |

| 1       | 0            | 0          | 1         | 1 1     | 1                                                            | 0                                                 |  |  |

| 1       | 1            | 1          | 1 1       | 1       | 1 1                                                          | 0                                                 |  |  |

|         |              |            | 37        | 0       | 0                                                            | 0                                                 |  |  |

|         | ogic<br>mbol |            | 1         | #       |                                                              |                                                   |  |  |

| Formula |              | C = A • B  | C = A + B | C = A⊕B | $C = \overline{A} + \overline{B}$ $C = \overline{A \cdot B}$ | $C = \overline{A \cdot B}$ $C = \overline{A + B}$ |  |  |

- 1. List the names of the six basic logic gates.

- a.

- b.

- C.

- d.

- e.

- f.

- 2. In the following formula, C is true only when A is true and B is

$$C = A \cdot B$$

$$C = A \oplus B$$

Using binary 1s and 0s, complete the truth table for each of the following logic gates:

NAND

| Inputs |   | Output |  |

|--------|---|--------|--|

| Α      | В | С      |  |

|        |   |        |  |

|        |   |        |  |

|        |   |        |  |

NOR

| Inputs |   | Output |

|--------|---|--------|

| Α      | В | С      |

|        |   |        |

|        |   |        |

|        |   |        |

- 1. List the names of the six basic logic gates.

- a. AND

- b. OR

- c. XOR (exclusive OR)

- d. NOT (inverter)

- e. NAND

- f. NOR

- In the following formula, C is true only when A is true and B is not true (false).

$$C = A \cdot \overline{B}$$

In the following formula, C is a binary 0 and A is a binary 1. Therefore, B must be a binary 1.

$$C = A \oplus B$$

Using binary 1s and 0s, complete the truth table for each of the following logic gates:

NAND

| Inpu | its | Output |

|------|-----|--------|

| Α    | В   | C      |

| 0    | 0   | 1      |

| 0    | 1   | 1      |

| 1    | 0   | 1      |

| 1    | 1   | 0      |

NOR

| Inputs |   | Output |

|--------|---|--------|

| A      | В | С      |

| 0      | 0 | 1      |

| 0      | 1 | 0      |

| 1      | 0 | 0      |

| 1      | 1 | 0      |

- Match each of the following logic functions with the correct mathematical formula:

- a. AND

- ( )  $C = \overline{A} \cdot \overline{B}$

- b. OR

- ( ) C = A ⊕ B

- c. XOR

- ( )  $C = \overline{A} + \overline{B}$

- d. NOT

- ( ) C = A . B

- e. NAND

- ( ) C = A + B

- f. NOR

- ()  $C = \overline{C}$

- 6. Write the name of each logic gate represented by the symbols shown below:

\_\_\_\_

\_\_\_\_

Y----

\_\_\_\_

2.77

\_\_\_\_

- Match each of the following logic functions with the correct mathematical formula:

- a. AND

- (f)  $C = \overline{A} \cdot \overline{B}$

b. OR

- (c) C = A (+) B

- c. XOR

- (e)  $C = \overline{A} + \overline{B}$

- d. NOT

- (a) C = A B

- e. NAND

- (b) C = A + B

- f. NOR

- (d)  $C = \overline{C}$

- Write the name of each logic gate represented by the symbols shown below:

NOT

XOR

AND

NOR

NAND

OR

Write the mathematical formula for each of the following logic functions. Use "C" for the output and "A" and "B" for the inputs.

a. XOR \_\_\_\_\_

b. NAND \_\_\_\_\_

c. OR \_\_\_\_\_

d. AND \_\_\_\_\_

e. NOR \_\_\_\_\_

Six logic gates are shown below. In each case write in a binary 1 or 0 for the missing input condition(s) that will produce the output condition indicated.

9. Draw the gate that outputs a 0 when at least one input is a 1.

7. Write the mathematical formula for each of the following logic functions. Use "C" for the output and "A" and "B" for the inputs.

$$C = A \oplus B$$

$$C = \overline{A} + \overline{B} \text{ or } C = \overline{A \cdot B}$$

$$C = A + B$$

$$C = A \cdot B$$

$$C = \overline{A} \cdot \overline{B}$$

or  $C = \overline{A} + \overline{B}$

Six logic gates are shown below. In each case, write in a binary 1

or 0 for the missing input condition(s) that will produce the output

condition indicated.

9. Draw the gate that outputs a 0 when at least one input is a 1.

NOR

| - | E | Х | Ε | R | C | S | Е | S |

|---|---|---|---|---|---|---|---|---|

10. Draw the gate that outputs a 1 only when both inputs are a 1.

11. Draw the gate that outputs a 1 when only one of its inputs is a 1.

12. Draw the gate that outputs a 0 only when both inputs are a 1.

13. Draw the gate that outputs a 1 when at least one of its inputs is a 1.

14. Draw the gate that outputs the complement of the input.

10. Draw the gate that outputs a 1 only when both inputs are a 1.

11. Draw the gate that outputs a 1 when only one of its inputs is a 1.

12. Draw the gate that outputs a 0 only when both inputs are a 1.

13. Draw the gate that outputs a 1 when at least one of its inputs is a 1.

14. Draw the gate that outputs the complement of the input.

# **Basic Circuits**

### - OBJECTIVES -

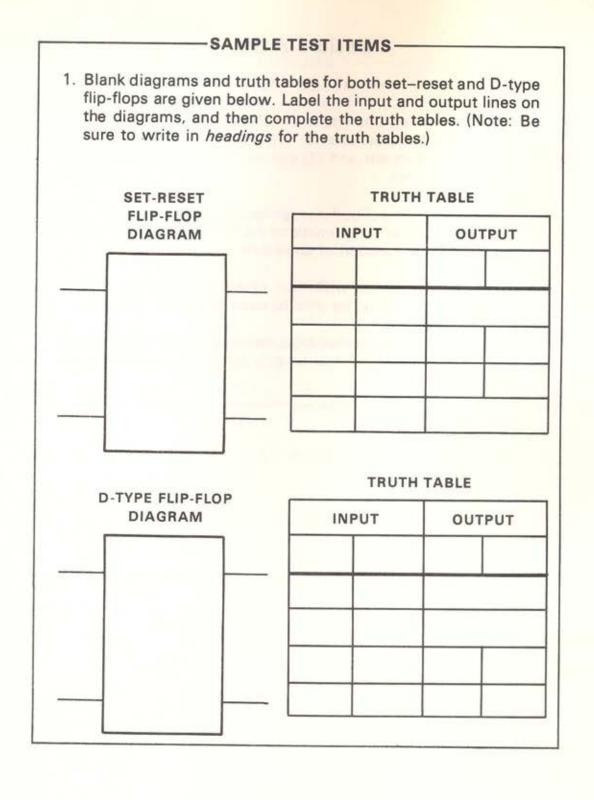

- Given blank diagrams and truth tables for both set-reset and D-type flip-flops, be able to: (1) label the input and output lines on the diagram, and (2) indicate in writing the elements of the truth table.

- Given the terms "buffer register," "shift register," and "counter," and several functions for each, be able to select the one proper function of each term.

- Given a logic circuit with four gates, one flip-flop, and a specific set of inputs, be able to write the circuit outputs.

- Given six terms related to logic, logic circuits, and hardware and a list of six definitions, be able to match each term with its definition.

## SAMPLE TEST ITEMS -

- 2. The buffer register:

- Permanently retains information for use in later programming.

- Momentarily slows down high-speed devices to allow lower-speed devices to handle output.

- Temporarily retains information until the selected unit is ready for it.

- d. Temporarily increases the speed of lower-speed devices to handle the output of faster devices.

- 3. For the logic circuits below, indicate the outputs for both Input A and Input B.

| Inpu | t A |

|------|-----|

|------|-----|

| ۸ |   | 4 |

|---|---|---|

| A | - | 1 |

$$B = 0$$

## Input B

$$A = 1$$

$$C =$$

## SAMPLE TEST ITEMS —

4. Match each of the terms below with its definition.

Term Definition

Truth Table \_\_\_\_

Don't Care \_\_\_\_

.

Definitions

- A particular output for a given set of inputs that is irrelevant.

- A means of expressing the input and output relationships of a logic circuit in tabular form.

•

Mark your place in this workbook and view Lesson 2 in the A/V program.

## Flip-Flops

A *flip-flop* is the basic electronic circuit used to store information in digital computers. This component is found in every type of digital computer. The flip-flop has two independent *stable* states and is capable of storing one bit of information, such as a bit in a word.

The flip-flop is capable of *storing* and *remembering* information. Its outputs are based on *past* input data as well as *current* input data. The flip-flop differs from the other logic gates we have examined; it can *store* data and *utilize* the stored data as well as current input data to specify the output generated. For this reason, the flip-flop is widely used in digital computers. The output of a logic gate depends *only* on present input; the output of a flip-flop depends on past, as well as present inputs.

When a flip-flop is set to one of its two stable states by an input pulse, it remains in that state when the input pulse is removed. Once a flip-flop is set to a specific state, it can only be changed to the opposite state by *another* different input pulse. This principle allows a flip-flop to store a bit value until the bit value is modified by a different input pulse.

The flip-flop operates like a toggle light switch that has an on and off state. Like the light switch, it must settle into one of these two states. It can never assume both states simultaneously. After you set the light switch with your finger, it remains in that state until you change it again with your finger.

There are a number of different types of flip-flops. The set-reset (RS) flip-flop and the clock-data or D-type flip-flop are two commonly used types. Both of these will be discussed in this lesson. Other types of flip-flop devices include the JK and the RST. All of these flip-flop devices operate in much the same manner, differing basically in the number and type of input lines.

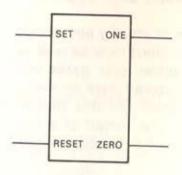

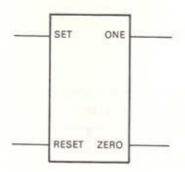

## Set-Reset (RS) Flip-Flops

As illustrated in Figure 13, an RS flip-flop has two input lines, the set line and the reset line, and two output lines, a ONE and a ZERO line. The labels "one" and "zero" for the output lines of a flip-flop tend to be confusing because these lines can carry either a binary 1 or 0 value. However, this line labeling convention is commonly used. To minimize confusion, output values will always be written as 1 or 0, while the output lines themselves will be labeled with names (ONE, ZERO).

Figure 13 Set-Reset Flip-Flop

When a binary 1 is applied to the reset line, a binary 0 is produced on the ONE line. The ZERO line always outputs the *opposite* value of the ONE line. That is, if there is a binary 1 on the ONE line, a binary 0 will appear on the ZERO line and vice versa. Since the output of a flip-flop remains stable until a different input pulse is applied, repeating the same binary pulse on an input line will have no effect. The flip-flop will remain unchanged until a different value on the input line causes a change in state.

Table 11 gives the truth table for a set-reset flip-flop. As you can see, the output on the ONE line and the output on the ZERO line are always opposite. The RS flip-flop should never receive a 1 input on both the set and reset lines simultaneously as the resulting output would be uncertain.

Table 11 Truth Table for an RS Flip-Flop

| IN  | PUT   | OU                     | TPUT |  |

|-----|-------|------------------------|------|--|

| SET | RESET | ONE                    | ZERO |  |

| 0   | 0     | No cha<br>(Same as pre |      |  |

| 0   | 1     | 0                      | 1    |  |

| 1   | 0     | 1                      | 0    |  |

| 1   | 1     | Uncert                 | ain  |  |

#### NOTE

Unlike the truth tables for logic gates, the truth tables for flip-flops contain a new entry: "no change."

## Clock-Data (D-type) Flip-Flops

D-type flip-flops save the binary value of a data line at some specific point in time. In order to accomplish this, the D-type flip-flop utilizes a control signal, called a *clock signal*, to specify when the binary data is to be stored. At that specified time, the data on the input line to the flip-flop is saved, regardless of the value already in the flip-flop.

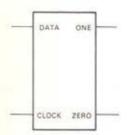

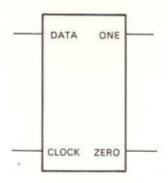

The D-type flip-flop resembles the set-reset flip-flop, but as indicated in Figure 14, the two input lines to this type of flip-flop are the DATA line and the CLOCK line.

Figure 14 D-type Flip-Flop

Table 12 Truth Table for a D-type Flip-Flop

| INF   | PUT  | OUT                   | PUT                                   |  |

|-------|------|-----------------------|---------------------------------------|--|

| CLOCK | DATA | ONE                   | ZERO                                  |  |

| 0     | 0    | No ch<br>(Same as pre | nange<br>vious output                 |  |

| 0     | 1    | No ch<br>(Same as pre | No change<br>(Same as previous output |  |

|       | 0    | 0                     | 1                                     |  |

| _1    | 1    | 1                     | 0                                     |  |

As with the RS flip-flop, the ZERO line output is always the opposite of the ONE line output.

- 1. How does a flip-flop differ from a logic gate?

- 2. List at least two types of flip-flops.

- In the space below, draw a simple diagram (logic symbol) of an RS flip-flop. Label all input and output lines.

4. For an RS flip-flop, given the input and output line values in the table below, fill in the output line values for the next output:

| 11  | NPUT  | ОИТ | PUT  |

|-----|-------|-----|------|

| SET | RESET | ONE | ZERO |

| 0   | 0     |     |      |

| 0   | 97001 |     |      |

| 1   | 0     |     |      |

| 1   | 1     |     |      |

1. How does a flip-flop differ from a logic gate?

A flip-flop can store and remember information. A logic gate depends only on current input information.

- 2. List at least two types of flip-flops.

- a. Set-reset (RS)

- D-type, clock-data

- c. JK

- d. RST

- In the space below, draw a simple diagram (logic symbol) of an RS flip-flop. Label all input and output lines.

4. For an RS flip-flop, given the input and output line values in the table below, fill in the output line values for the next output:

| 11  | NPUT  | OUTPUT    |      |  |

|-----|-------|-----------|------|--|

| SET | RESET | ONE       | ZERO |  |

| 0   | 0     | No change |      |  |

| 0   | 1     | 0         | 1    |  |

| 1   | 0     | 1         |      |  |

| 1   | 1     | Uncertain |      |  |

|   | P \ | / P |      | 0 | 10 | -   | • |

|---|-----|-----|------|---|----|-----|---|

| - | E/  | (E  | : 14 | C | 13 | E 3 | 5 |

5. What is the difference between an RS flip-flop and a D-type flip-flop?

Draw a simple diagram of a D-type flip-flop. Label all input and output lines.

7. For a D-type flip-flop, given the input and output line values in the table below, fill in the output line value for the next output.

| IN             | PUT | ОИТ       | PUT  |

|----------------|-----|-----------|------|

| CLOCK DATA 0 0 |     | ONE       | ZERO |

|                |     | No change |      |

| 0              | 1   |           |      |

| <b>_</b>       | 1   |           |      |

|                | 0   |           |      |

5. What is the difference between an RS flip-flop and a D-type flip-flop?

The D-type flip-flop assumes the state of the DATA input when a clock *pulse* appears at its CLOCK input. The RS flip-flop does *not* have a CLOCK input. Instead, the RS flip-flop is set or reset by a binary 1 *level* appearing at its SET input or RESET input. If the RS flip-flop receives a 1 at both its SET and RESET inputs, its state is uncertain.

Draw a simple diagram of a D-type flip-flop. Label all input and output lines.

7. For a D-type flip-flop, given the input and output line values in the table below, fill in the output line value for the next output.

| IN       | PUT  | ОИТ       | PUT  |

|----------|------|-----------|------|

| CLOCK    | DATA | ONE       | ZERO |

| 0        | 0    | No change |      |

| 0        | 1    | No change |      |

| <u>_</u> | 1    | 1         |      |

| <u>+</u> | 0    | 0         | 1    |

## Registers

Flip-flops can be interconnected to form more complex computer circuits. Some of these circuits will be discussed in Appendix A.

As we discussed, each flip-flop can store only one bit of information. However, more than one bit is required to make a computer word. Consequently, a group of flip-flops must be joined together to form a register.

A register is used to store the binary representation of a number, control information, or some other pattern of bits that the computer uses. Registers provide temporary, fast-access storage for data and addresses. Computers generally use a number of different registers. Each register performs a specific function in the data processing operation or in the control of the computer.

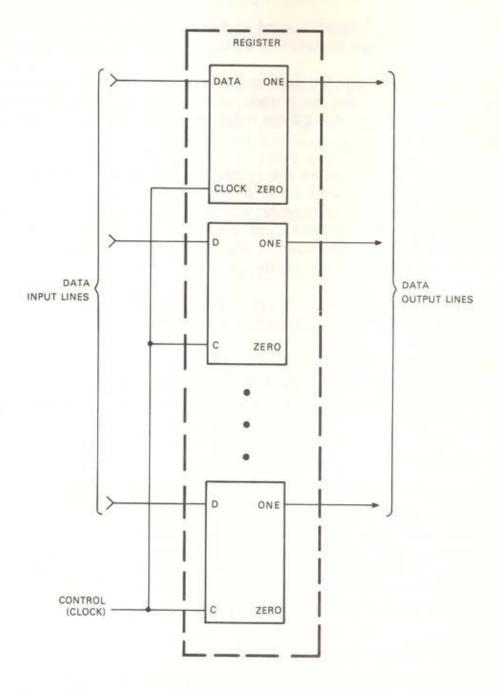

These registers can be made up of any type of flip-flop. Figure 15 illustrates a register using D-type flip-flops with an input and output line for each bit.

# **Buffer Registers**

Some parts of the computer, such as the central processing unit, process information at extremely high speeds, while other units operate at lower speeds. In order to compensate for the lower speed and to avoid keeping a high-speed device waiting, special registers, called buffer registers, located in the individual units, temporarily retain information until the selected unit is ready to utilize it. Maximum utilization of the computer can be attained by using buffer registers.

# Shift Registers

We have discussed registers that are used for storage and information transfer only. Another type of register is the shift register. Shift registers perform an important additional operation on stored information. A shift register can *shift* its entire contents one or more bit positions to the right or left. As a result of the shift operation, data can be fed into one end of the register, one bit at a time, and then shifted through the register as needed.

Figure 15 Register Using D-Type Flip-Flops

By shifting the contents of the shift register one place to the *left*, this register *multiplies* the contents of the register by 2. Conversely, shifting the contents of the shift register one position to the *right* is equivalent to *dividing* the entire contents by 2. Thus, the shift register performs mathematical operations simply by shifting the contents of the register. Positions at the right end of the register that are vacated as a result of the shift (least significant bits) are usually filled with zeros. Positions on the left are usually filled with the value that was in the leftmost (most significant) bit before the shift. Figure 16 illustrates the use of the shift register in multiplication and division. When used for division, the least significant bits are lost as a result of the right shift operation.

Figure 16 Shift Register Showing Multiply and Divide Arithmetic Operations

Like other types of registers, shift registers are constructed of flip-flops.

#### Counters

Counters are circuits that count the number of binary 1 inputs. They consist of combinations of flip-flops.

There are two kinds of counters: *up-counters* and *down-counters*. Up-counters start at zero and *increment* by one each time a binary 1 is input in the counter. The counter continues to increase as long as the binary 1s are received.

Down-counters work in the opposite direction. Here, the first number in the counter is the highest number, and the counter decrements until its contents read zero.

Counters are used to control various computer functions such as: counting the number of binary 1s on an input line to determine if the correct number has been received; controlling the number of shifts performed by the shift register; and maintaining an up-to-date record of an event, such as the number of words transferred from main memory to auxiliary storage.

|     | _ |          | - |  |

|-----|---|----------|---|--|

| EVE | _ | $\sim$ 1 |   |  |

| EXE | ĸ |          | - |  |

| -/- |   | ~ 1      | - |  |

| 1. | Ma | atch these terms<br>ter of the term in | wi | th t | the appropriate definition by placing the arentheses next to the correct definition.  |

|----|----|----------------------------------------|----|------|---------------------------------------------------------------------------------------|

|    | a. | Counter                                | (  | )    | Moves stored bits to the right or left.                                               |

|    |    | D-type flip-flop                       | (  | )    | Compensates for time differences during data transfers within the computer.           |

|    |    | Buffer register Shift register         | (  | )    | Binary 1 input increments or decrements the contents by 1.                            |

|    |    |                                        | (  | )    | Repeating the same binary value on the DATA line will have no effect.                 |

| 2. | W  | nich of the following                  | ng | are  | the basic storage elements of a register?                                             |

|    | a. | AND gates                              |    |      |                                                                                       |

|    | b. | OR gates                               |    |      |                                                                                       |

|    | c. | XOR gates                              |    |      |                                                                                       |

|    | d. | Flip-flops                             |    |      |                                                                                       |

| 3. |    |                                        |    |      | needed to store data, temporarily, from a outer until a lower speed unit is ready for |

|    | a. | Shift register                         |    |      |                                                                                       |

|    | b. | Counter                                |    |      |                                                                                       |

|    | C. | Buffer register                        |    |      |                                                                                       |

|    | d. | Logic gate                             |    |      |                                                                                       |

| SO | LU | ITI | 0 | NS  |

|----|----|-----|---|-----|

| ~~ | -  |     | - | 140 |

- Match these terms with the appropriate definition by placing the letter of the term in the parentheses next to the correct definition.

- a. Counter

- (d) Moves stored bits to the right or left.

- b. D-type flip-flop

- (c) Compensates for time differences during data transfers within the computer.

- c. Buffer register

- d. Shift register

- (a) Binary 1 input increments or decrements the contents by 1.

- (b) Repeating the same binary value on the DATA line will have no effect.

- 2. Which of the following are the basic storage elements of a register?

- a. AND gates

- b. OR gates

- c. XOR gates

- (d.) Flip-flops

- 3. Which type of register is needed to store data, temporarily, from a high-speed unit of a computer until a lower speed unit is ready for it?

- Shift register

- b. Counter

- (c.) Buffer register

- d. Logic gate

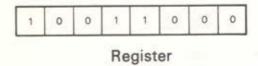

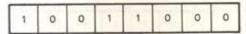

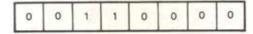

Given an 8-bit shift register with the initial data as shown, insert the data in the shift register as it would appear after the shifts indicated are performed.

- a. Shift right two bit places

- b. Shift left one bit place

- 5. The binary equivalent of the number 28 is stored in a shift register. A shift right two bit places is executed. The number in the shift register is now:

- a. 28

- b. 14

- c. 7

- d. 56

Given an 8-bit shift register with the initial data as shown, insert the data in the shift register as it would appear after the shifts indicated are performed.

a. Shift right two bit places

| 0 0 | 1 | 0 | 0 | 1 | 1 | 0 |

|-----|---|---|---|---|---|---|

|-----|---|---|---|---|---|---|

b. Shift left one bit place

- 5. The binary equivalent of the number 28 is stored in a shift register. A shift right two bit places is executed. The number in the shift register is now:

- a. 28

- b. 14

- ©. 7

- d. 56

|     | -      | - | -   | -    |

|-----|--------|---|-----|------|

| EXE | - 60 / |   | 621 | - 60 |

|     |        |   |     |      |

- 6. Select as many of the following as typify possible uses for a counter:

- a. Shifting data right or left

- Maintaining a record of the number of bits transferred within the computer

- c. Indicating the number of binary 1s on an input line

- d. Keeping track of the number of times a shift is performed.

- 7. The current value in an up-counter is 6. Two more counts are made. What value is now present in the counter?

- a. 8

- b. 6

- c. 2

- d. 4

| 00 | 1 1 | 170 | 0 | B. II | 0 |

|----|-----|-----|---|-------|---|

| SO | LU  |     | U | N     | 2 |

- 6. Select as many of the following as typify possible uses for a counter:

- a. Shifting data right or left

- (b) Maintaining a record of the number of bits transferred within the computer

- c. Indicating the number of binary 1s on an input line

- d. Keeping track of the number of times a shift is performed

- 7. The current value in an up-counter is 6. Two more counts are made. What value is now present in the counter?

- (a.) 8

- b. 6

- c. 2

- d. 4

Take the test for this module and evaluate your answers before studying another module.

# Appendix A More Complex Circuits

# Combining Logic Elements

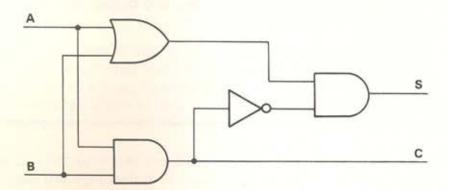

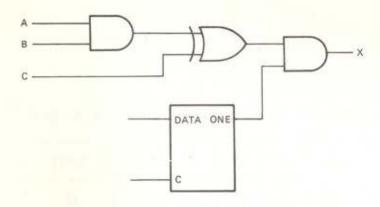

Performing arithmetic and logic operations on data is one of the basic functions of a computer. These operations are done by electronic circuits using various combinations of *logic gates*, *flip-flops*, and *registers*. In this section, we will demonstrate the way in which the *logic elements* discussed thus far can be combined into *logic circuits* that can be used to perform some of these important logic and arithmetic operations.

In our examples, only logic gates AND, OR, XOR and NOT and the set-reset and D-type flip-flops will be used in the logic circuits. In practice, many different kinds of logic elements are used in logic circuits.

## Adder Circuit

One of the principal operations in the digital computer is the addition of two numbers. With the computer, numbers are represented in *binary* form. To understand the method used by the computer to execute this basic function, we will design a simple logic circuit that will take two binary digits and perform an addition operation.

First, we will review binary arithmetic. The addition operation is quite simple because there are only *two* digits in the binary system. As shown in the following example, there are just four possible combinations:

Three of the four possible combinations yield simple, single-digit sums. However, in the fourth case, a carry is generated to the *next* digit position.

These arithmetic examples can be expressed in tabular form known as a truth table. In the following truth table, A and B represent the two inputs, and S and C represent the sum and carry digits, respectively.

Table 13 Truth Table for Binary Arithmetic

| Input |   | Output |  |

|-------|---|--------|--|

| Α     | В | С      |  |

| 0     | 0 | 0      |  |

| 0     | 1 | 0      |  |

| 1     | 0 | 0      |  |

| 1     | 1 | 1      |  |

| Inp | ut | Output |  |  |

|-----|----|--------|--|--|

| Α   | В  | S      |  |  |

| 0   | 0  | 0      |  |  |

| 0   | 1  | 1      |  |  |

| 1   | 0  | 1      |  |  |

| 1   | 1  | 0      |  |  |

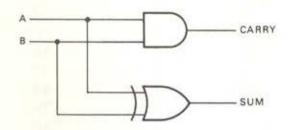

Examining the carry digit first, it becomes apparent that we have a carry *only* when *both* line A and line B have an input of 1. The logic element that produces this result is the AND gate. The carry circuit would be as shown in Figure 17.

| В | С |

|---|---|

| 0 | 0 |

| 1 | 0 |

| 0 | 0 |

| 1 | 1 |

|   | 1 |

Figure 17 Carry Circuit

The sum circuit is more complex. The sum is 1 if either line A or line B has an input of 1, but not if both have an input of 1. The logic circuit to perform this function, therefore, must produce a 1 value when the A input is 1 and the B input is 0 or when the A input is 0 and the B input is 1.

Examining the truth table for the sum circuit, we can see that it is identical to the XOR gate. This logic circuit is shown in Figure 18.

| Α | В | SUM |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

Figure 18 Sum Circuit for Binary Addition

The second circuit we designed, the sum circuit, reveals an interesting phenomenon. As you can see, when the *two* inputs are *identical*, the output is *always* a 0, and when they are *different*, the output is always a 1. This circuit is often called a binary *comparator* because it actually compares two values.

A combination of the carry circuit and the sum circuit, which is illustrated in Figure 19, is called a *half-adder* circuit. Two of these half-adder circuits are needed in order to perform binary addition with two binary digits as input; hence, the name *half-adder*.

Figure 19 Half-Adder Logic Circuit

## Tracing a Logic Circuit

To test or repair computers, it is frequently necessary to determine the output of a logic circuit for a given set of inputs. If the logic circuit is complex, this can be a very tedious and time-consuming task. This section discusses how to trace a logic circuit by showing simple examples of up to four logic gates and one flip-flop to demonstrate this principle.

# Two Logic Gate Circuit

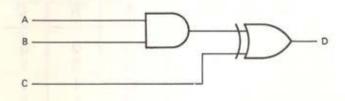

To trace a logic circuit completely, the truth table for this circuit should be constructed. Figure 20 illustrates the 3-input logic circuit with a 2-input AND gate and a 2-input XOR gate connected.

Figure 20 3-Input Logic Circuit

To specify this circuit completely, we must first list all possible input values. In this context, specify involves tabulating all the possible input and output values. Since there are three inputs to this circuit, each of which can be a 1 or 0, we have 2<sup>3</sup> (or 8) possible input values. Table 14 lists the number of possible input values for up to eight input lines.

Table 14 Input Values

| Number of<br>Input Lines | Number of Possible<br>Input Values |  |  |

|--------------------------|------------------------------------|--|--|

| 1                        | 2                                  |  |  |

| 2                        | 4                                  |  |  |

| 2 3                      | 8                                  |  |  |

| 4                        | 16                                 |  |  |

| 5                        | 32                                 |  |  |

| 6                        | 64                                 |  |  |

| 7                        | 128                                |  |  |

| 8                        | 256                                |  |  |

As this table illustrates, the number of input values doubles every time the number of input lines increases by one. There must be a row in the truth table for each value of the input as the number of input lines increases by one. This is another indication of how tedious it could be to attempt to construct a truth table for a logic circuit of any size or complexity.

In the example, eight rows are required for the truth table. There is a special method of listing the input values in a truth table to avoid accidentally omitting any input value. First, the row number is listed, beginning with 0. Then the binary number value for that row is entered as shown in Table 15. In this way, every possible input value is listed consecutively.

Table 15

|            | Input Value |   |   |  |  |

|------------|-------------|---|---|--|--|

| Row Number | Α           | В | С |  |  |

| 0          | 0           | 0 | 0 |  |  |

| 1          | 0           | 0 | 1 |  |  |

| 2          | 0           | 1 | 0 |  |  |

| 3          | 0           | 1 | 1 |  |  |

| 4          | 1           | 0 | 0 |  |  |

| 5          | 1           | 0 | 1 |  |  |

| 6          | 1           | 1 | 0 |  |  |

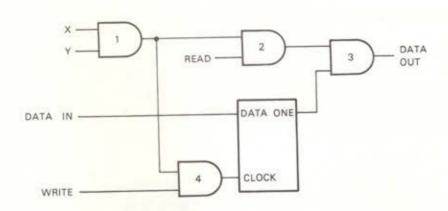

| 7          | 1           | 1 | 1 |  |  |